## Transimpedance Amplifiers with 133 GHz bandwidth on 130nm InP DHBT

S. Giannakopoulos, Z. He, I. Darwazeh and H. Zirath

In this work we present two transimpedance amplifier (TIA) circuits designed for fibre optical interconnect systems. We compare a common base (CB) topology with a common emitter (CE) shunt-shunt feedback topology in terms of frequency response, power consumption, noise and input impedance. The two TIAs are designed on a 130nm InP DHBT technology from Teledyne Scientific Company (TSC) with an  $f_U f_{max}$  of 520 GHz/1.15 THz and are measured in the frequency and time domains. They exhibit a TI-gain of 42 dB $\Omega$  with a 133 GHz bandwidth, the highest bandwidth reported in literature and a power consumption of 32.3 mW for the CB and 25.5 mW for the CE. Eye diagram measurements were conducted up to 64 Gbps and input referred noise density was measured at 30.2 pA/ $\sqrt{Hz}$  for the CB and 13.9 pA/ $\sqrt{Hz}$  for the CE.

Introduction: The continual increase of internet traffic and the expansion of the field of high performance computing systems are driving the demands for higher interconnect bandwidth and energy efficiency in datacenters and supercomputing clusters. The high data rate in combination with the requirement to minimise power consumption has allowed the field of short-haul optical interconnects (OI) to develop into one of the fastest growing branches in the OI market. In order to facilitate such electro-optical links, a new generation of integrated transmitter and receiver systems are required.

This work presents two transimpedance amplifier circuits, which when integrated with a photodiode, can operate as front-ends of OI receiver systems. In such systems bandwidth is mainly limited by the optoelectronic transceiver components, namely the transmitter VCSEL diodes [1] and the receiver photodiodes. In order to extend the bandwidth of the receiver, architectures with low input impedance were preferred [2]. The circuits were fabricated in a 130nm InP DHBT process by TSC with an fv/fmax of 520 GHz/1.15 THz [3]. The outline of this paper is as follows: we present the design and implementation of the two TIA MMICs, then we discuss the measurements in the frequency and time domains, and we compare obtained results with state of the art literature and we conclude the paper.

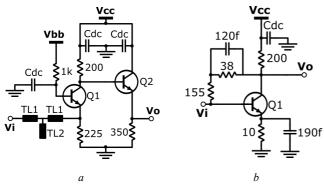

Design: The common emitter (CE) with shunt feedback topology provides adequate gain, relatively low input impedance and good noise performance. The common base (CB) topology provides higher voltage gain for the same current and low input impedance, however it suffers from increased noise. Fig. 1a shows the CB topology used in this work, along with an input matching open stub and a common collector (CC) stage used as an output buffer. In Fig. 1b the schematics of the CE design is shown where the feedback resistor is split into two resistors, one of them bypassed by a capacitor to increase feedback at and reduce peaking at higher frequencies. Additionally, an emitter resistor with a capacitive bypass was used to extend the bandwidth by limiting the gain. In the case of the CE TIA no CC stage was used as a buffer, rather the output was taken directly from the node Vo.

Fig. 1 Schematics of the two TIAs. Resistor values are given in Ohm and capacitor values in Farad. Decoupling capacitor Cdc is equal to 750 fF. a Schematic of the Common Base TIA.  $V_{cc} = 3.6 \text{ V}$ ,  $I_{cc} = 8.9 \text{ mA}$ ,  $V_{bb} = 1.4 \text{ V}$ ,  $I_{bb} = 0.18 \text{ mA}$ .

b Schematic of the Common Emitter TIA.  $V_{cc} = 3 \text{ V}$ ,  $I_{cc} = 8.75 \text{ mA}$ .

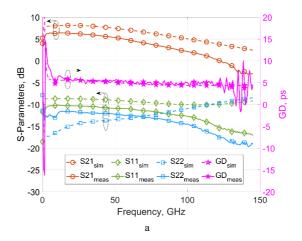

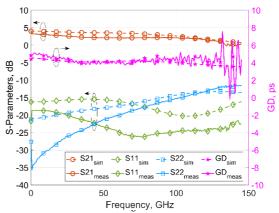

Fig. 2 S-parameter (left axis) and group delay (right axis) results for the two TIAs. The dashed lines indicated simulated response.

a Common Base circuit and b Common Emitter circuit.

Measurements: The S-parameter on wafer measurements (100 MHz – 145 GHz) were done with an Anritsu ME7838A vector network analyzer (VNA) with included dc-block capacitors via coaxial Cascade Infinity 67 GHz GSG probes. The input power was set to -30 dBm to avoid saturating the TIAs.

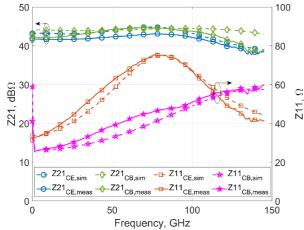

The frequency domain measurements show good agreement with the simulated results. Comparing the S-parameter response of the CB and CE TIAs in Fig. 2 we see that the main difference lies on the voltage gain. The CB has a gain of 6.3 dB with a bandwidth of 80 GHz while the CE has a gain of 3.2 dB up to 130 GHz. The input and output reflection of both designs were below -10 dB, and the group delay was flat on the entirety of the bandwidth with very little variation. The Z-parameters calculated from the S-parameter measurements of the two designs (seen in Fig. 3) show a transimpedance gain (Z21) of 42 dB $\Omega$  on both designs with the CB providing 2.5 dB of peaking. The main difference of the two topologies is in their input impedance (Z11) with the CB presenting an impedance 25  $\Omega$  and less than 50  $\Omega$  up to 80 GHz, while the CE 35  $\Omega$  and less than 50  $\Omega$  up to 40 GHz. The input impedance of the CB-design can be further reduced to 10 ohm, without changing the bandwidth significantly. This can be done by increasing the emitter length of Q1, since Q1 in this design is operated at very high current density, where the transconductance is limited due to high current injection effects. The input impedance variation is critical as it dictates the bandwidth which is dependent, amongst other factors, on the photodiode capacitance at the input of the TIA.

Time domain measurements were done on wafer using two Cascade infinity 67-GHz GSGSG probes. A 64-Gbaud PRBS-15 datastream generated by the SHF 12103A pattern generator (PPG), was fed to the input of the device under test (DUT). The voltage swing of the data was set to 600 mV to get the best performance out of the PPG and was attenuated down to 30 mV through 26 dB attenuators in order to avoid saturating the input of the TIAs. Additionally, AC coupling capacitors were used at the input and output ports.

Fig. 3 Z-parameter results for the two different topologies.

The output of the DUT was connected to the input of an 86100C Agilent Infinium DCA-J 70 GHz sampling oscilloscope. The noise measurements were carried out with the histogram function of the oscilloscope by leaving the input of the DUT open.

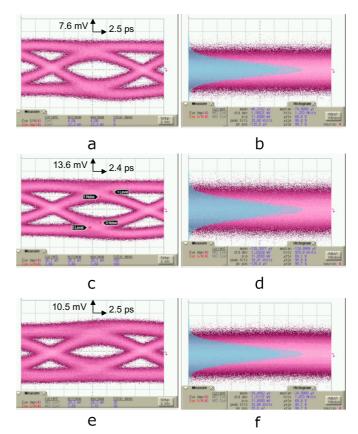

Fig. 4 shows the eye diagrams (left) and noise histograms (right). Fig. 4a-b show the waveform generated by the SHF pattern generator after the attenuator and dc-block coupled in the oscilloscope, essentially the input signal of the DUTs. The voltage signal to noise ratio (SNR) of the input eye is 4 and the noise standard deviation ( $\sigma_n$ ) is 1.17 mV. Fig. 4c-d show the response of the CB TIA with an SNR of 3.66 and a  $\sigma_n$  of 1.33 mV. Fig.4e-f show the response of the CE TIA with SNR of 3.1 and a  $\sigma_n$  of 1.21 mV. The CE topology has lower voltage gain (as indicated also from Fig. 2) and lower noise. The CB circuit provides higher gain, at the expense of its increased noise which is characteristic of the common base amplifier topology [2]. Based on the measured eye diagrams the circuits have an energy efficiency of 0.5 pJ/bit for the CB and 0.4 pJ/bit for the CE.

Comparison with state-of-the-art: The comparison of the performance of the designed TIAs with the state of the art in reported in open literature is presented in Table 1. Both proposed designs have the highest bandwidth reported. It is worth noting that the TIAs designed of this work would represent only the input stages of a full receiver, therefore the total transimpedance gain is lower than many of those reported with post-amplifiers. For the same reason the power consumption is lower relative to the other amplifiers, with the exception of a similar design in [6]. The noise performance of the CB is worse than amplifiers with higher input impedance, as expected from a common base topology. The CE TIAs noise, however, is significantly lower than most of the state-of-the-art designs, at the expense of the higher input impedance.

Conclusion: We present the design and measurement of two TIAs of different topologies, CB and CE, suitable for next generation optical interconnects. The TIAs, designed on a 130nm InP DHBT process by TSC demonstrate trade-offs between low noise, power consumption and low input impedance. Both designs have a TI-bandwidth higher than 133 GHz, which is the highest reported in literature, to the best of our knowledge.

**Table 1:** Comparison with state of the art TIAs in literature.

| Ref. | BR<br>Gbps | Power<br>mW | TI BW<br>GHz | TI gain<br>dBΩ | $\frac{IRN}{pA} \frac{pA}{\sqrt{Hz}}$ |

|------|------------|-------------|--------------|----------------|---------------------------------------|

| [4]  | 43         | 304         | 110          | 50             | -                                     |

| [5]  | 40         | 36.5        | 108          | 46             | 53.9                                  |

| [6]  | -          | 48          | 92           | -              | 17.7                                  |

| [7]  | -          | 27.6        | 72           | 38             | 84.1                                  |

| [8]  | 100        | 150         | 66           | 65             | 8                                     |

| CB   | 64         | 32.3        | 133          | 42             | 30.2                                  |

| CE   | 64         | 25.5        | 133          | 42             | 13.9                                  |

Fig. 4 Eye diagrams and noise histograms (left) for the oscilloscope output and the output of the two TIAs.

Acknowledgments: This work was supported by the Swedish Foundation for Strategic Research (SSF). The MMICs were fabricated by TSC.

S. Giannakopoulos, Z. He and H. Zirath (Department of Microtechnology and Nanoscience, Chalmers University of Technology, Gothenburg, Sweden)

E-mail: stagia@chalmers.se

I. Darwazeh (Department of Electronic & Electrical Engineering, University College London, London, UK)

## References

- 1. Westbergh P., et al. "High-speed 850 nm VCSELs with 28 GHz modulation bandwidth operating error-free up to 44 Gbit/s." Electronics Letters 48.18 (2012): 1145-1147.

- 2. Wilson B., and I. Darwazeh. "Transimpedance optical preamplifier with a very low input resistance." Electronics Letters 23.4 (1987): 138-139

- 3. Urteaga, M., et al. "THz InP bipolar transistors-circuit integration and applications." Compound Semiconductor Integrated Circuit Symposium (CSICS), 2017 IEEE. IEEE, 2017.

- 4. C. H. Fields et al., "110+ GHz Transimpedance Amplifier in InP-HBT Technology for 100 Gbit Ethernet," IEEE Microwave and Wireless Components Letters, vol. 20, no. 8, pp. 465–467, Aug. 2010. 5. J. Kim and J. F. Buckwalter, "Staggered Gain for 100+ GHz Broadband Amplifiers," IEEE Journal of Solid-State Circuits, vol. 46, no. 5, pp. 1123–1136, May 2011.

- 6. K. Vasilakopoulos, S. P. Voinigescu, P. Schvan, P. Chevalier, and A. Cathelin, "A 92GHz bandwidth SiGe BiCMOS HBT TIA with less than 6dB noise figure," in 2015 IEEE Bipolar/BiCMOS Circuits and Technology Meeting BCTM, Boston, MA, USA, 2015, pp. 168–171. 7. J. Chong and D. S. Ha, "A 100 Gb/s transimpedance amplifier with diode-connecting input-resistance-reduction in 32 nm CMOS technology," in 2015 IEEE 58th International Midwest Symposium on Circuits and Systems (MWSCAS), 2015, pp. 1–4.

- 8. I. G. López, A. Awny, P. Rito, M. Ko, A. C. Ulusoy, and D. Kissinger, "100 Gb/s Differential Linear TIAs With Less than 10 pA/ $\sqrt{\text{Hz}}$  in 130-nm SiGe:C BiCMOS," IEEE Journal of Solid-State Circuits, vol. 53, no. 2, pp. 458–469, Feb. 2018.