# New Strategies for Low Noise, Agile PLL Frequency Synthesis

by

## Hongyu Wang

A thesis submitted to the University College London for the Degree of Doctor of Philosophy in Electronic Engineering

Department of Electronic & Electrical Engineering

University College London

March 2009

| I, Hongyu Wang, confirm that the work presented in this thesis is my own. Where information has been derived from other sources, I confirm that this has been indicated in the thesis and |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| acknowlegements.                                                                                                                                                                          |

| Hongyu Wang                                                                                                                                                                               |

|                                                                                                                                                                                           |

|                                                                                                                                                                                           |

|                                                                                                                                                                                           |

|                                                                                                                                                                                           |

|                                                                                                                                                                                           |

To my Parents and Rui.

#### **Abstract**

Phase-Locked Loop based frequency synthesis is an essential technique employed in wireless communication systems for local oscillator generation. The ultimate goal in any design of frequency synthesisers is to generate precise and stable output frequencies with fast switching and minimal spurious and phase noise. The conflict between high resolution and fast switching leads to two separate integer synthesisers to satisfy critical system requirments.

This thesis concerns a new sigma-delta fractional-*N* synthesiser design which is able to be directly modulated at high data rates while simultanously achieving good noise performance. Measured results from a prototype indicate that fast switching, low noise and spurious free spectra are acheved for most covered frequencies. The phase noise of the unmodulated synthesiser was measured –113 dBc/Hz at 100 kHz offset from the carrier.

The intermodulation effect in synthesisers is capable of producing a family of spurious components of identical form to fractional spurs caused in quantisation process. This effect directly introduces high spurs on some channels of the synthesiser output. Numerical and analytic results describing this effect are presented and amplitude and distribution of the resulting fractional spurs are predicted and validated against simulated and measured results. Finally an experimental arrangement, based on a phase compensation technique, is presented demonstrating significant suppression of intermodulation-borne spurs.

A new technique, pre-distortion noise shaping, is proposed to dramatically reduce the impact of fractional spurs in fractional-N synthesisers. The key innovation is the introduction in the bitstream generation process of carefully-chosen set of components at identical offset frequencies and amplitudes and in anti-phase with the principal fractional spurs. These signals are used to modify the  $\Sigma$ - $\Delta$  noise shaping, so that fractional spurs are effectively cancelled. This approach can be highly effective in improving spectral purity and reduction of spurious components caused by the  $\Sigma$ - $\Delta$  modulator, quantisation noise, intermodulation effects and any other circuit factors. The spur cancellation is achieved in the digital part of the synthesiser without introducing additional circuitry. This technique has been convincingly demonstrated by simulated and experimental results.

# **Acknowledgements**

The work presented in this thesis could not have happened without the help and support of many people. First of all, I would like to express my appreciation of my supervisor, Professor Paul V. Brennan, for bringing this interesting and useful problem to me, for making available his valuable time on a regular basis to discuss the progress of the project and also for his professional guidance and very useful suggestions through out the project. He also provided help in technical writing style and presentation style, and I found it to be extremely valuable. The skills that I learned from him will be of much use to me in my whole life and thus I am in gratitude for his supervision.

I would like to give a special thanks to Dr. Dai Jiang for his guidance and friendship during my time here. He introduced me to a lot of useful theories. His expert suggestions on both electronic circuits and radio frequency system design directed me a short way.

Finally, greatly thanks to Engineering and Physical Sciences Research Council (EPSRC) for providing the financial support which made this work possible.

# **Table of Contents**

| Abstract        |                                                                                                 | 4  |

|-----------------|-------------------------------------------------------------------------------------------------|----|

| Acknowled       | gements                                                                                         | 5  |

| Table of Co     | ntents                                                                                          | 6  |

| List of Figur   | es                                                                                              | 8  |

| List of Princ   | ipal Symbols                                                                                    | 13 |

| List of Abbr    | eviations                                                                                       | 15 |

| Chapter 1       | ntroduction                                                                                     | 17 |

| 1.1 Th          | e Issue of Frequency Synthesis                                                                  | 17 |

| 1.2 Th          | esis Scope and Contributions                                                                    | 19 |

| 1.3 Th          | esis Outline                                                                                    | 21 |

| 1.4 Au          | thor's Publications                                                                             | 22 |

| Chapter 2       | Phase-Locked Loop Fundamentals                                                                  | 24 |

| 2.1 Int         | roduction to Phase-Locked Loops                                                                 | 24 |

| 2.2 Ph          | ase-Locked Loop Elements                                                                        | 26 |

| 2.2.1           | Phase/Frequency Detector                                                                        |    |

| 2.2.2           | Voltage Controlled Oscillator                                                                   |    |

| 2.2.3           | Frequency Divider                                                                               |    |

|                 | eger-N Synthesisers<br>op Filter                                                                |    |

| 2.4 LO<br>2.4.1 | First Order type I Loops                                                                        |    |

| 2.4.1           | Second Order Type II Loops                                                                      |    |

| 2.4.3           | Third Order Type II Loops                                                                       |    |

| 2.5 Ac          | quisition                                                                                       | 46 |

| 2.6 Su          | mmary                                                                                           | 50 |

| Chapter 3       | Sigma-Delta Fractional-N Frequency Synthesis                                                    | 51 |

| 3.1 Int         | roduction                                                                                       | 51 |

| 3.2 Fre         | equency Dividers                                                                                | 56 |

| 3.2.1           | Dual-Modulus Dividers                                                                           |    |

| 3.2.2           | Multi-Modulus Dividers                                                                          |    |

|                 | gma-Delta Modulators                                                                            |    |

| 3.3.1<br>3.3.2  | Introduction to Sigma-Delta Modulation in Frequency Synthesis First Order Sigma-Delta Modulator |    |

| 3.3.3           | MASH 1-1-1                                                                                      |    |

| 3.3.4           | MASH 2-2                                                                                        | 69 |

| 3.3.5           | Single-Stage Sigma-Delta Modulators with Feedforward                                            |    |

| 3.3.6<br>3.4 Mo | Single-Stage Sigma-Delta Modulators with Feedback<br>odelling Synthesiser Phase Noise           |    |

| 3.4.1           | Noise Sources                                                                                   |    |

| 3.4.2           | ADS Noise Model                                                                                 |    |

|                 |                                                                                                 |    |

| 3.4.3          | Matlab Noise Model                                           | 85  |

|----------------|--------------------------------------------------------------|-----|

| 3.5            | Summary                                                      | 89  |

| Chapter 4      | Novel Synthesiser Designs and Measured Results               | 90  |

| 4.1            | Design Considerations                                        | 90  |

| 4.1.1          |                                                              |     |

| 4.1.2          | Synthesiser Requirements in Base Stations                    |     |

| 4.2 N<br>4.2.1 | Memory Controlled Frequency Dividers                         |     |

| 4.2.2          |                                                              |     |

| 4.3 F          | FPGA Implementation of Sigma-Delta Modulators                | 100 |

|                | ow Reference Frequency Fractional-N Synthesiser              |     |

| 4.5 H          | High Reference Frequency Fractional-N Synthesiser            | 118 |

| Chapter 5      | Coupling and Intermodulation-Induced Spurs and Their Suppres |     |

|                |                                                              |     |

|                | The Intermodulation Effect – General Description             |     |

|                | Spur Distribution Analysis and Amplitude Prediction          |     |

| 5.2.1<br>5.2.2 | Numerical SimulationAnalytic Method                          |     |

| 5.2.3          | Stability Threshold                                          | 141 |

|                | Comparison with Modelled and Measured Results                |     |

|                | Spur Suppression Techniques and Measured Results             |     |

|                | Summary                                                      |     |

| Chapter 6      | Pre-Distortion Sigma-Delta Noise Shaping                     | 157 |

| 6.1 I          | ntroduction                                                  | 157 |

|                | Noise Shaping and Spurious Component Analysis                |     |

|                | The Proposed Technique                                       |     |

|                | Experimental Setup and Results                               |     |

|                | Summary                                                      |     |

| Chapter 7      | Conclusions and Further Work                                 | 175 |

|                | Conclusions                                                  |     |

| 7.2 F          | Future work                                                  | 178 |

| Reference      | es                                                           | 181 |

| Appendix       | A RF Board Design                                            | 187 |

| A.1 Ove        | erview                                                       | 187 |

| A.2 Sch        | ematics and Layout                                           | 187 |

| Appendix       | B Matlab Routines                                            | 192 |

|                | ma-delta PSD Simulation                                      |     |

| J              | upling-induced VCO Discrete Spurs                            |     |

|                | thesiser Phase Noise Simulation                              |     |

| B.4 Clos       | sed Loop Response                                            | 198 |

| B.5 Ste        | p Response of PLLs                                           | 200 |

# **List of Figures**

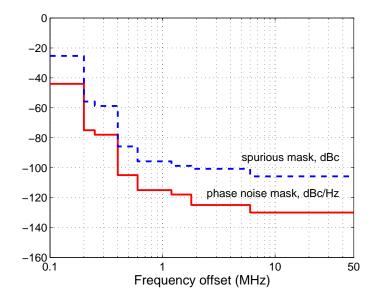

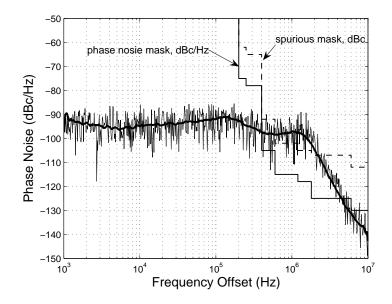

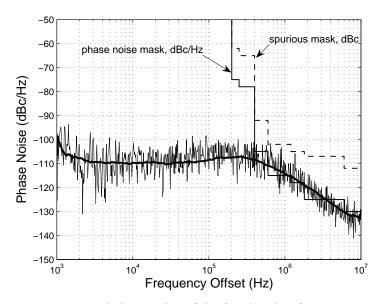

| Figure 1.1  | GSM specification masks.                                                                                                                 | 20 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------|----|

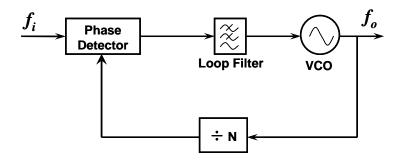

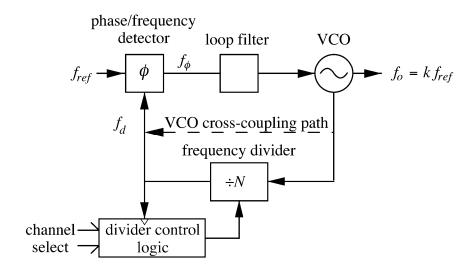

| Figure 2.1  | A block diagram of the basic arrangement of a Phase-Locked Loop.                                                                         | 26 |

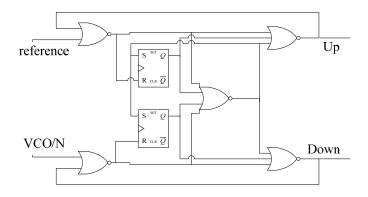

| Figure 2.2  | Functional diagram of a phase/frequency detector.                                                                                        | 27 |

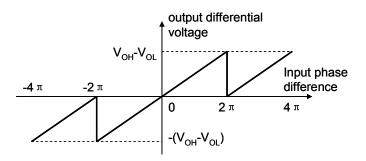

| Figure 2.3  | The PFD output voltage versus phase difference.                                                                                          | 27 |

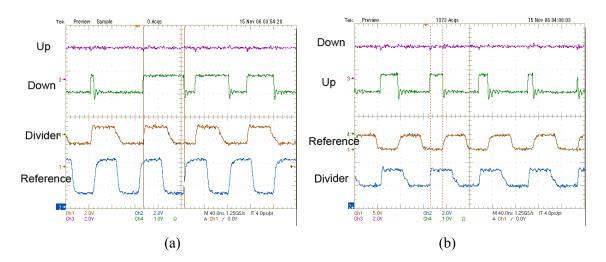

| Figure 2.4  | Measured waveforms of the Phase/Frequency Detector. (a) Divider output lags reference signal. (b) Reference signal lags divider output.  | 28 |

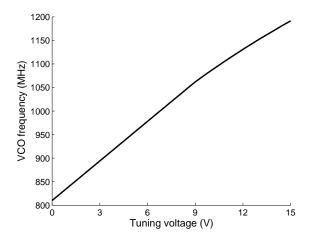

| Figure 2.5  | Measured tuning characteristic of a low-noise VCO Z-COMM CLV1025E.                                                                       | 30 |

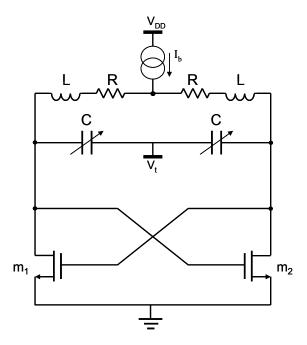

| Figure 2.6  | Circuit diagram of an LC-tank VCO.                                                                                                       | 30 |

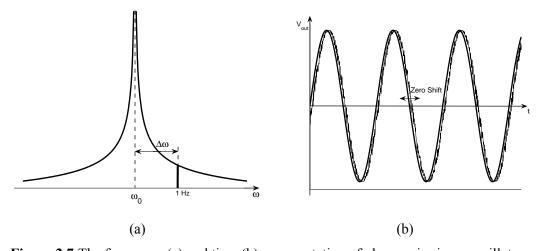

| Figure 2.7  | The frequency (a) and time (b) representation of phase noise in an oscillator.                                                           | 31 |

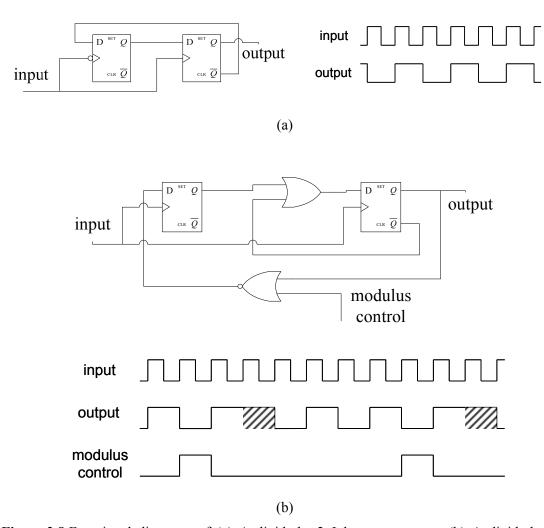

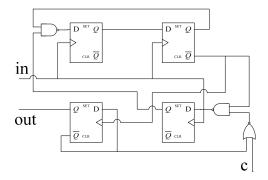

| Figure 2.8  | Functional diagrams of (a) A divide-by-2 Johnson counters. (b) A divide-by-2/3 circuit implemented by logic gates and D-type flip-flops. | 33 |

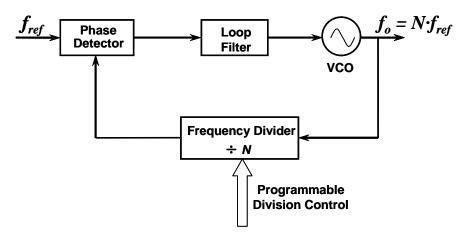

| Figure 2.9  | A general arrangement of an integer-N synthesiser.                                                                                       | 34 |

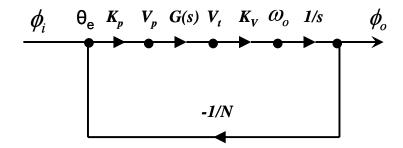

| Figure 2.10 | Signal flow graph representation of a PLL.                                                                                               | 36 |

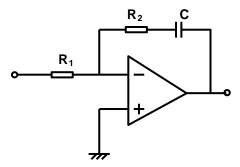

| Figure 2.11 | Single input second order type II loop filter.                                                                                           | 39 |

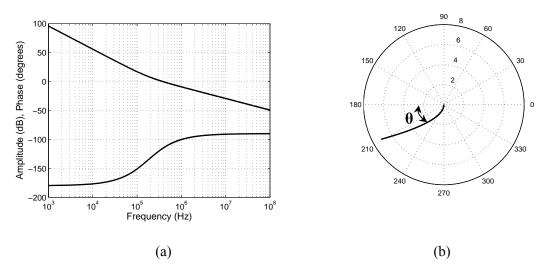

| Figure 2.12 | Amplitude and phase of open loop complex phase response.                                                                                 | 41 |

| Figure 2.13 | Amplitude and phase of closed loop complex phase response.                                                                               | 41 |

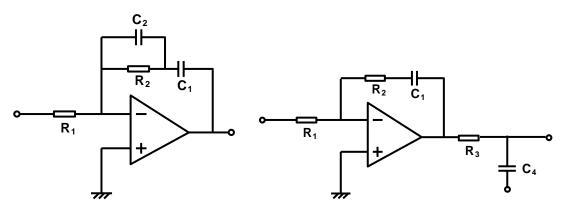

| Figure 2.14 | Two topologies of single input third order type II loop filters.                                                                         | 42 |

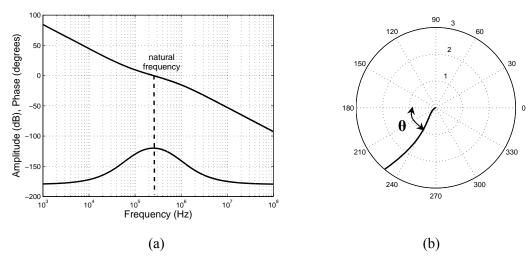

| Figure 2.15 | Amplitude and phase of open loop complex phase response.                                                                                 | 45 |

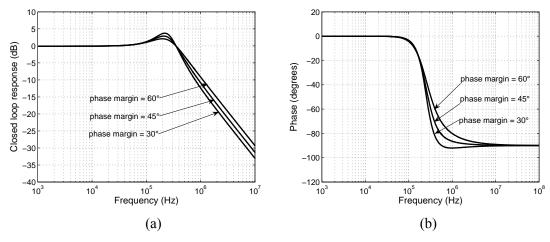

| Figure 2.16 | Amplitude and phase of closed loop complex phase response.                                                                               | 45 |

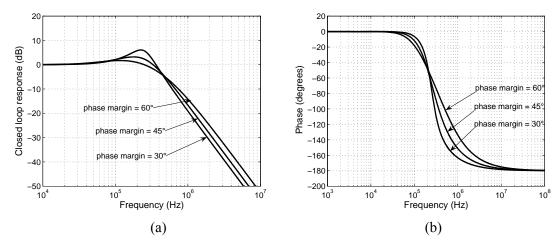

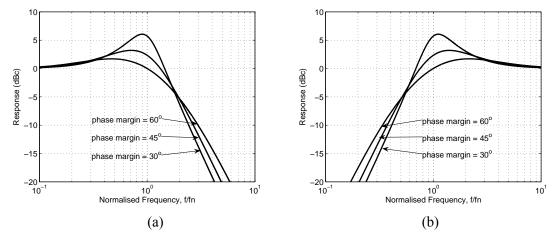

| Figure 2.17 | Modulation of loop for phase margin of 30, 45 and 60 degrees. (a) Phase modulation response. (b) Frequency modulation response.          | 46 |

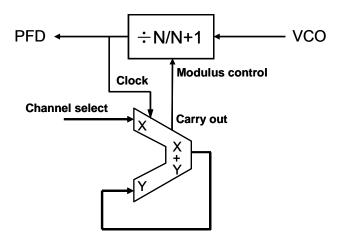

| Figure 3.1  | The Fractional-N frequency divider controlled by a digital accumulator.                                                                  | 52 |

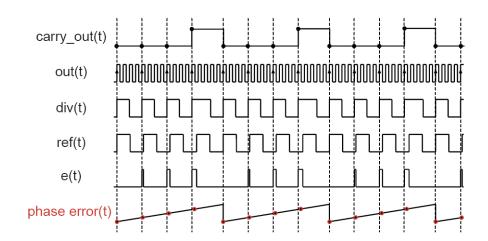

| Figure 3.2  | The time diagram of the VCO and frequency divider output, carry out and phase error for $n = 0.25$ .                                     | 54 |

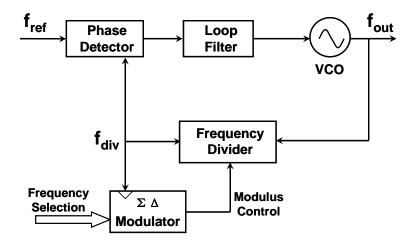

| Figure 3.3  | A typical arrangement of a $\Sigma$ - $\Delta$ fractional- $N$ frequency synthesiser.                                                    | 55 |

| Figure 3.4  | A divide-by-8/9 dual-modulus divider.                                                                                                    | 57 |

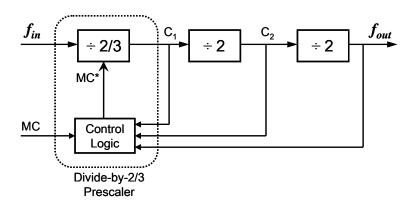

| Figure 3.5  | Logical architecture of a divide-by-8/9 prescaler.                                                                                       | 58 |

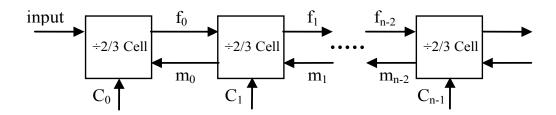

| Figure 3.6  | The architecture of a conventional ripple fashion divider.                                                                               | 59 |

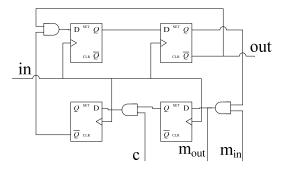

| Figure 3.7  | A divide-by-2/3 cell in ripple fashion dividers.                                                                                         | 59 |

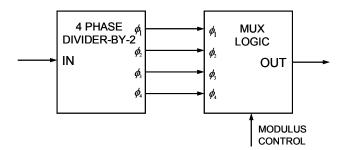

| Figure 3.8  | The architecture of a multi-modulus phase switching prescaler.                                                                           | 61 |

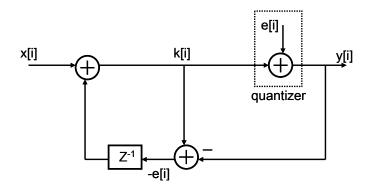

| Figure 3.9  | Time domain function diagram of a basic $\Sigma$ - $\Delta$ modulator.                                                                   | 63 |

| Figure 3.10 | First-order $\Sigma$ - $\Delta$ modulator with error-feedback topology.                                                                  | 64 |

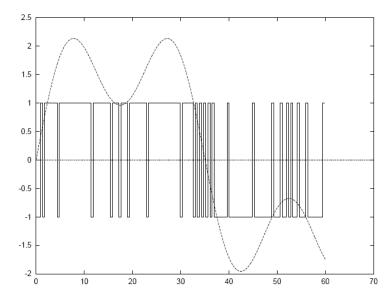

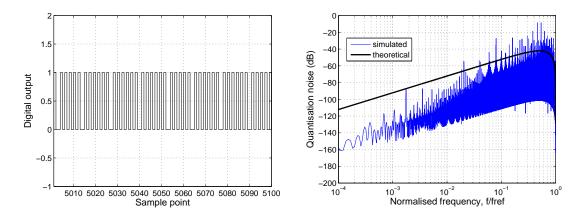

| Figure 3.11 | Time domain output and quantisation noise of a first-order $\Sigma$ - $\Delta$ modulator.                                                | 65 |

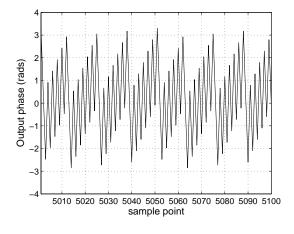

| Figure 3.12 | Phase error of the first-order $\Sigma$ - $\Delta$ modulator.                                                                            | 65 |

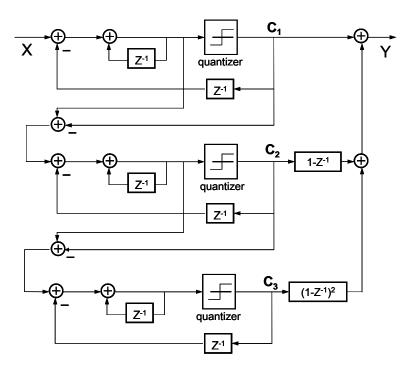

| Figure 3.13 | Block diagram of a MASH 1-1-1 $\Sigma$ - $\Delta$ modulator                                                                              | 66 |

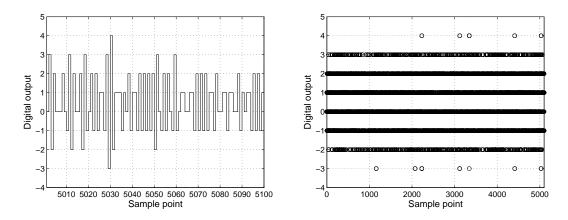

| Figure 3.14 | Time domain output and distribution of a MASH 1-1-1 $\Sigma$ - $\Delta$ modulator.                                                       | 68 |

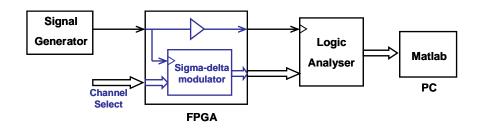

| Figure 3.15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A setup for $\Sigma$ - $\Delta$ modulator time domain output measurements. <b>68</b>                                                                                                                                  |     |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

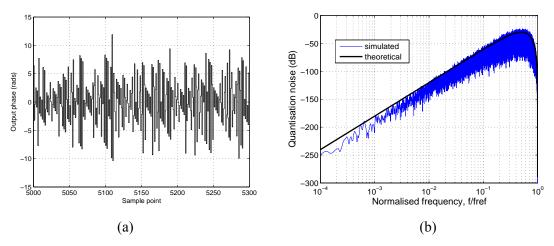

| Figure 3.16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Phase error (a) and theoretical and simulated PSD (b) of the MASH 1-1-1 $\Sigma$ - $\Delta$ 68 modulator.                                                                                                             |     |  |  |  |

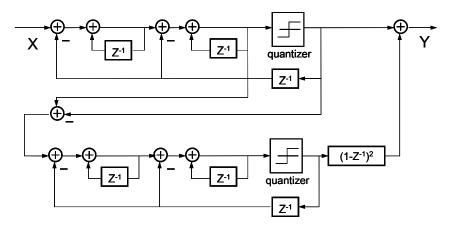

| Figure 3.17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Block Diagram of a cascaded 2-2 MASH $\Sigma$ - $\Delta$ modulator 69                                                                                                                                                 |     |  |  |  |

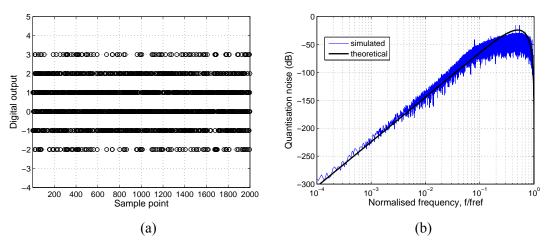

| Figure 3.18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Output distribution (a) and theoretical and simulated PSDs (b) of MASH 2-2 $\Sigma$ - $\Delta$ modulator.                                                                                                             |     |  |  |  |

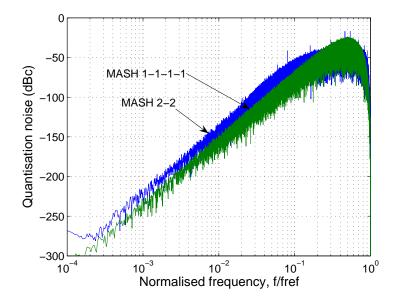

| Figure 3.19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PSD comparison of MASH 2-2 and MASH 1-1-1-1 Σ-Δ modulators. <b>70</b>                                                                                                                                                 |     |  |  |  |

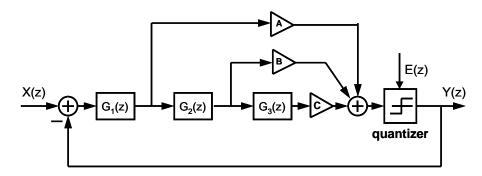

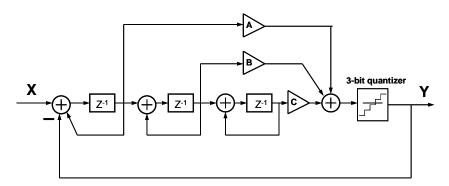

| Figure 3.20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Block diagram of a third order $\Sigma$ - $\Delta$ modulator with feedforward.                                                                                                                                        | 71  |  |  |  |

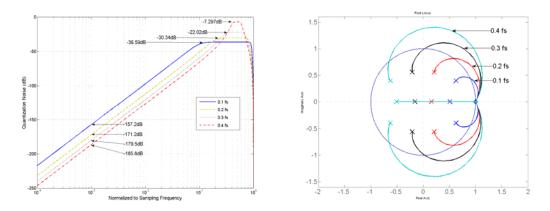

| Figure 3.21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | NTF and stability of Butterworth high pass topology.                                                                                                                                                                  |     |  |  |  |

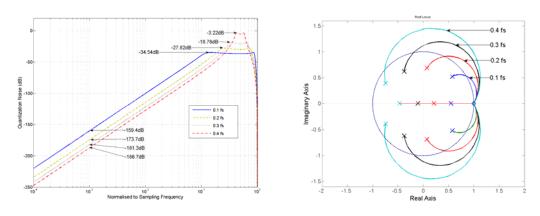

| Figure 3.22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | NTF and stability of Chebyshev type II high pass filter.                                                                                                                                                              | 73  |  |  |  |

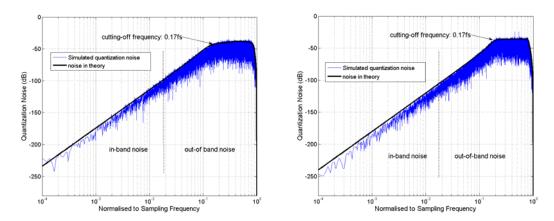

| Figure 3.23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PSDs of $\Sigma$ - $\Delta$ modulators based on Butterworth (left) and Chebyshev type II (right) high pass theories with the same cut-off frequency of 0.17 fs.                                                       | 74  |  |  |  |

| Figure 3.24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | An implemented third order feedforward $\Sigma\text{-}\Delta$ modulators based on Butterworth characteristic.                                                                                                         | 74  |  |  |  |

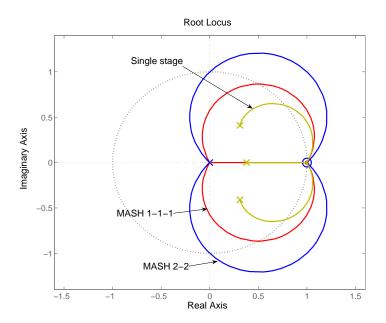

| Figure 3.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Root locus and poles of the NTF.                                                                                                                                                                                      | 75  |  |  |  |

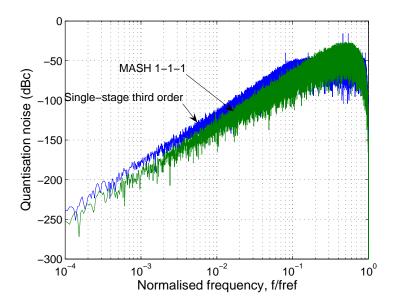

| Figure 3.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PSD comparison of MASH 1-1-1 and single stage $\Sigma$ - $\Delta$ modulators.                                                                                                                                         | 75  |  |  |  |

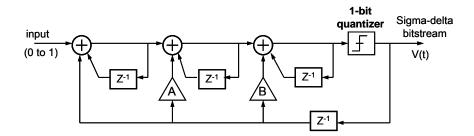

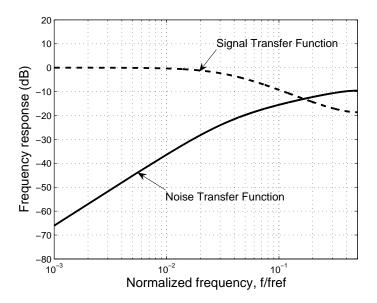

| Figure 3.27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A typical third-order single-bit feedback $\Sigma$ - $\Delta$ modulator.                                                                                                                                              | 76  |  |  |  |

| Figure 3.28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Modelled frequency response of signal transfer function and noise transfer function of the third order single-bit $\Sigma$ - $\Delta$ modulator.                                                                      |     |  |  |  |

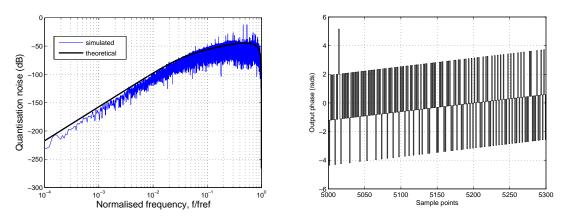

| Figure 3.29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PSD and phase error of the third order single stage modulator.                                                                                                                                                        | 77  |  |  |  |

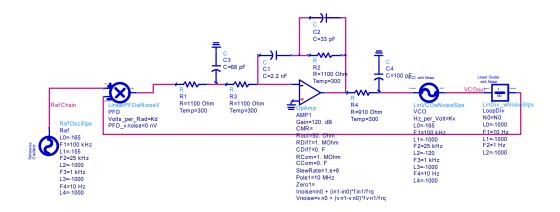

| Figure 3.30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A HP ADS model of a third-order type II phase-locked loop. 83                                                                                                                                                         |     |  |  |  |

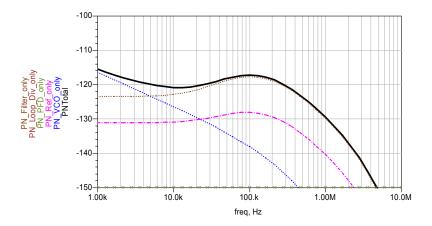

| Figure 3.31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Contributions to VCO phase noise in an integer- <i>N</i> synthesiser. <b>84</b>                                                                                                                                       |     |  |  |  |

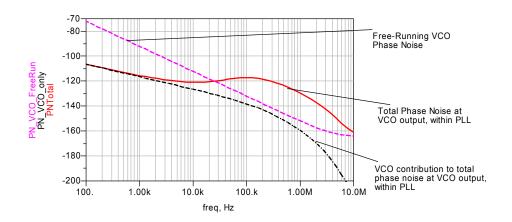

| Figure 3.32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Loop reduction of VCO phase noise.                                                                                                                                                                                    |     |  |  |  |

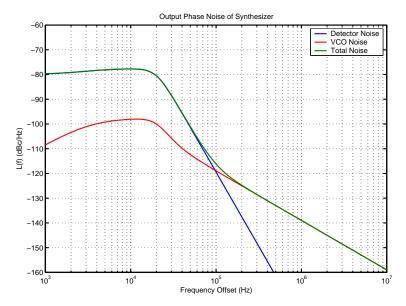

| Figure 3.33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Modelled integer- <i>N</i> synthesiser phase noise.                                                                                                                                                                   |     |  |  |  |

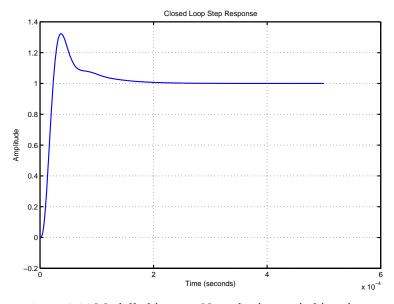

| Figure 3.34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Modelled integer- <i>N</i> synthesiser switching time.                                                                                                                                                                |     |  |  |  |

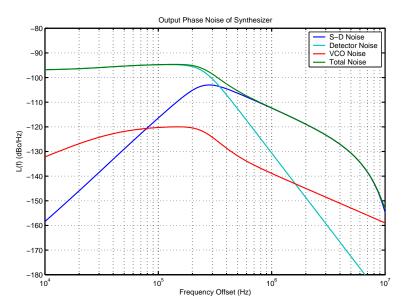

| Figure 3.35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Modelled fractional- <i>N</i> synthesiser phase noise, with 13 MHz reference <b>87</b> frequency.                                                                                                                     |     |  |  |  |

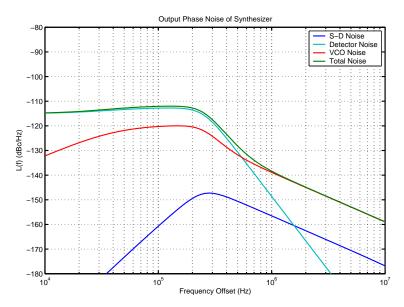

| Figure 3.36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Modelled fractional- $N$ synthesiser phase noise, with 100 MHz reference frequency.                                                                                                                                   | 88  |  |  |  |

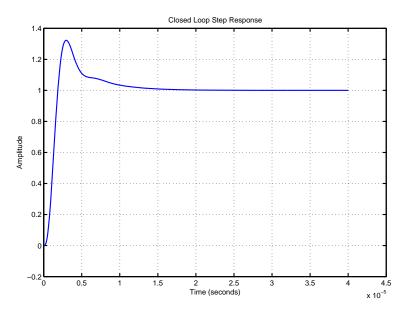

| Figure 3.37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Modelled fractional-N synthesiser switching time.                                                                                                                                                                     | 88  |  |  |  |

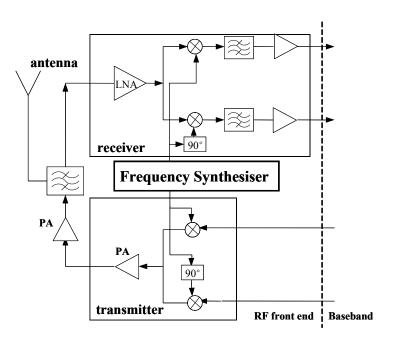

| Figure 4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | A general arrangement of GSM transceivers.                                                                                                                                                                            | 91  |  |  |  |

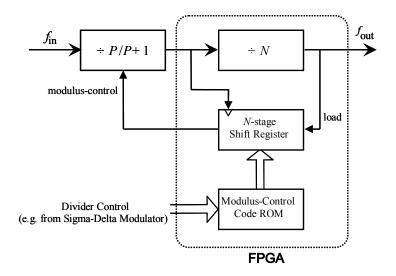

| Figure 4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | The proposed memory-controlled divider, with a division ratio of $NP$ to $N(P+1)$ .                                                                                                                                   |     |  |  |  |

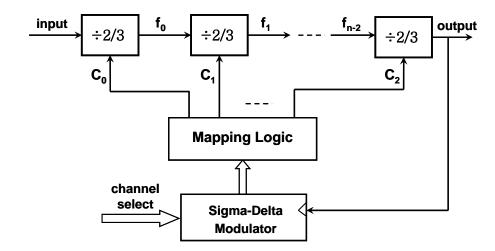

| Figure 4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | A general memory-controlled multi-modulus divider.                                                                                                                                                                    | 95  |  |  |  |

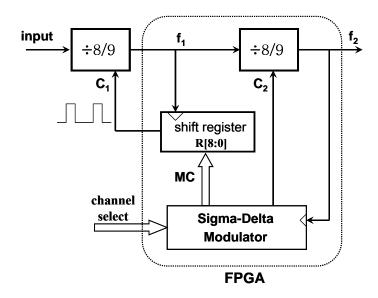

| Figure 4.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | A memory-controlled 18-modulus divider suitable for GSM systems.                                                                                                                                                      | 98  |  |  |  |

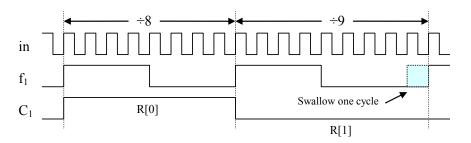

| Figure 4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Modulus control function of the $\div$ 8/9 block.                                                                                                                                                                     |     |  |  |  |

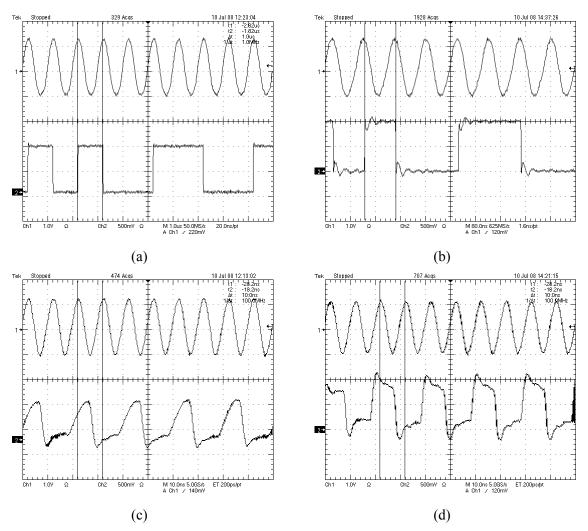

| Figure 4.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Time domain output of the FPGA implemented $\Sigma$ - $\Delta$ modulator. (a) Sampling frequency: 1 MHz. (b) Sampling frequency: 10 MHz. (c) Sampling frequency: 100 MHz. (d) Sampling frequency: 100 MHz with XCITE. | 104 |  |  |  |

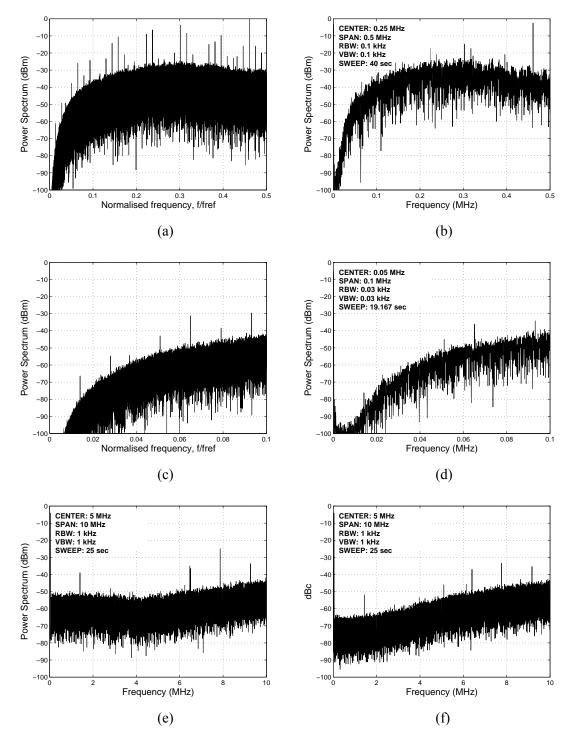

| Figure 4.7 Modelled and measured noise shaping of the FPGA implemented $\Sigma$ modulator. (a) Modelled noise shaping, span: $0.5f_{ref}$ . (b) Measured noise shaping at 1 MHz sampling frequency, span: $0.5f_{ref}$ . (c) Modelled noise shaping, span: $0.1f_{ref}$ . (d) Measured noise shaping under 1 MHz sampling frequency, span: $0.1f_{ref}$ . (e) Measured noise shaping at 100 MHz sampling frequency, without XCITE. (f) Measured noise shaping at 100 MHz sampling frequency, with XCITE. |                                                                                                                                                                                                                       | 105 |  |  |  |

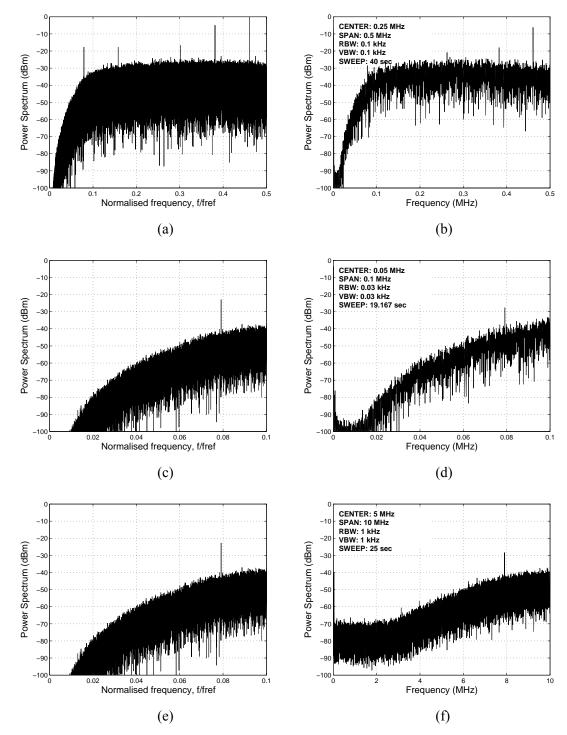

| Figure 4.8  | Modelled and measured noise shaping of the FPGA implemented Butterworth single-stage $\Sigma$ - $\Delta$ modulator. (a) Modelled noise shaping, span: $0.5f_{ref}$ . (b) Measured noise shaping at 1 MHz sampling frequency, span: $0.5f_{ref}$ . (c) Modelled noise shaping, span: $0.1f_{ref}$ . (d) Measured noise shaping at 1 MHz sampling frequency, span: $0.1f_{ref}$ . (e) Modelled noise shaping, span: $0.1f_{ref}$ . (f) Measured noise shaping at 100 MHz sampling frequency, with XCITE. | 106 |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

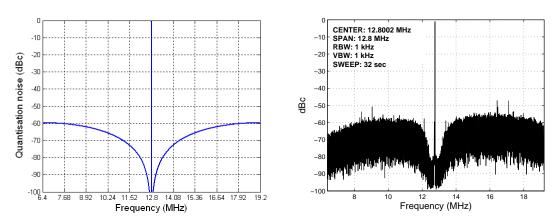

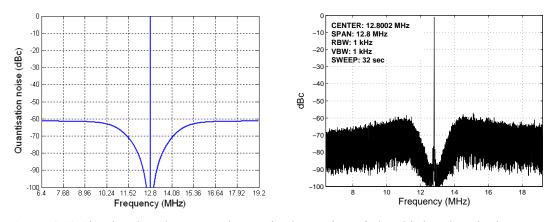

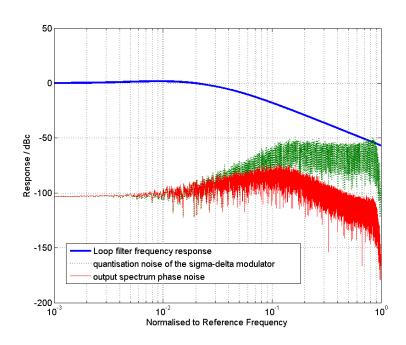

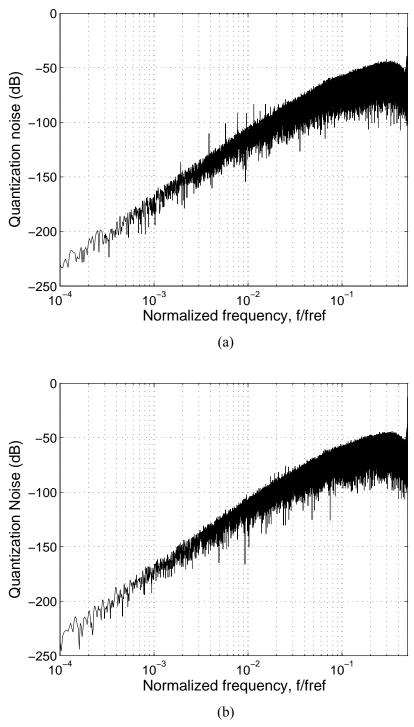

| Figure 4.9  | Simulated and measured quantisation noise of the MASH 2-2 $\Sigma$ - $\Delta$ modulator.                                                                                                                                                                                                                                                                                                                                                                                                               | 107 |  |  |

| Figure 4.10 | Simulated and measured quantisation noise of the third order single stage $\Sigma\text{-}\Delta$ modulator.                                                                                                                                                                                                                                                                                                                                                                                            | 107 |  |  |

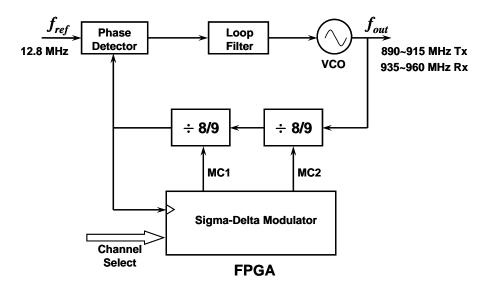

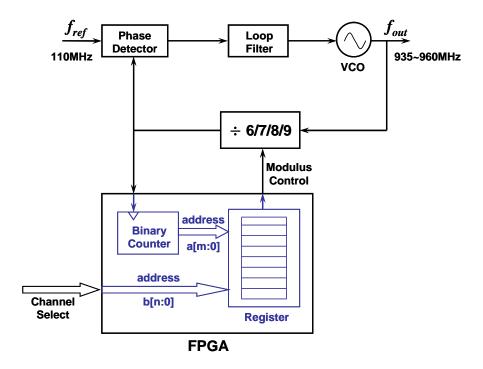

| Figure 4.11 | Block diagram of an implemented high division ratio fractional-N synthesiser.                                                                                                                                                                                                                                                                                                                                                                                                                          | 109 |  |  |

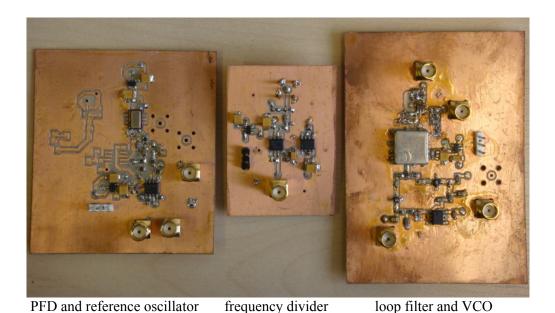

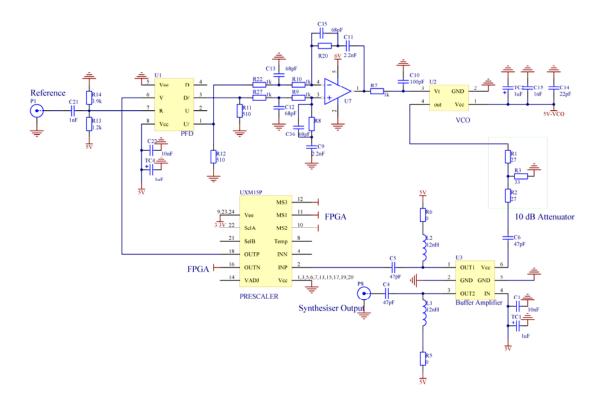

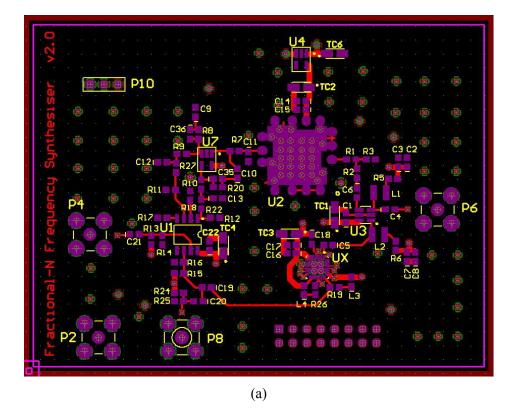

| Figure 4.12 | RF section of a fractional-N synthesiser implemented on discrete PCBs.                                                                                                                                                                                                                                                                                                                                                                                                                                 | 110 |  |  |

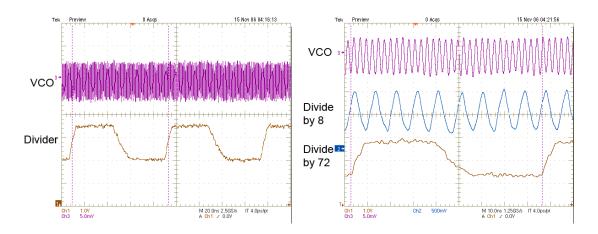

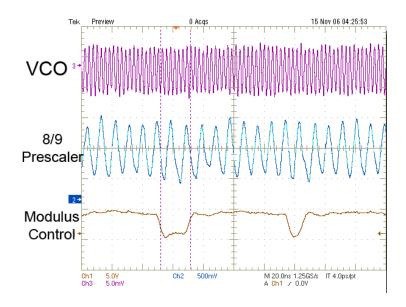

| Figure 4.13 | Time domain outputs of the VCO and frequency divider.                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 110 |  |  |

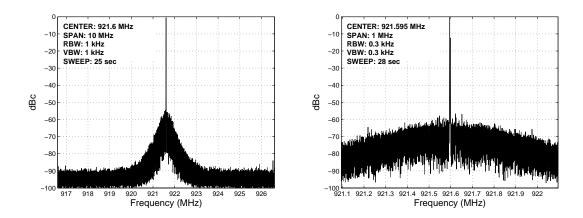

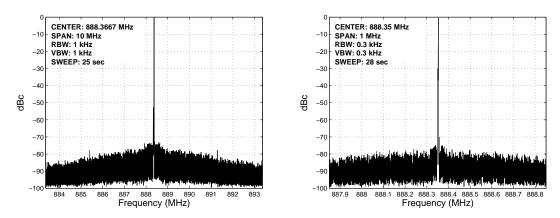

| Figure 4.14 | Measured spectra of the integer synthesiser with 10 MHz span (left) and 1 MHz span (right).                                                                                                                                                                                                                                                                                                                                                                                                            | 111 |  |  |

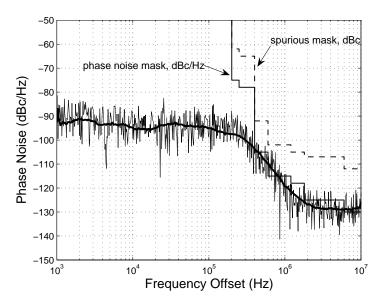

| Figure 4.15 | Measured phase noise of the integer synthesiser.                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 111 |  |  |

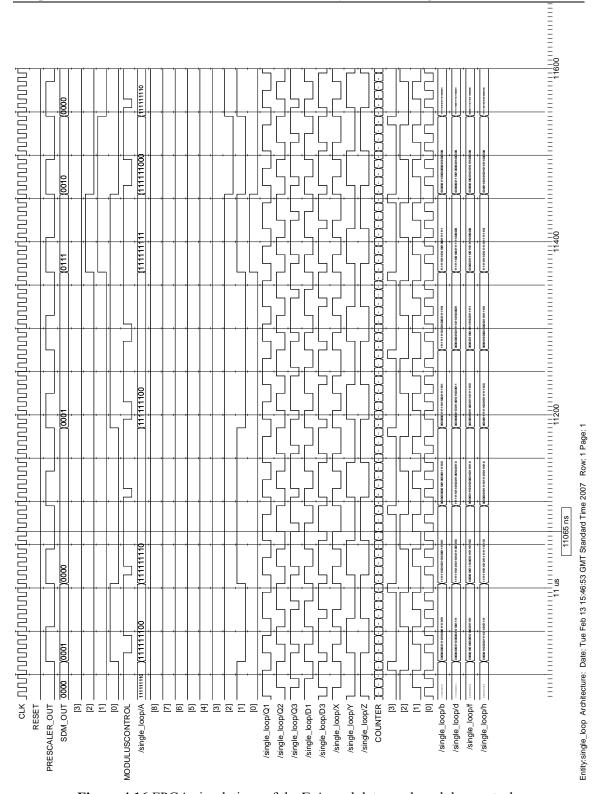

| Figure 4.16 | FPGA simulations of the $\Sigma\text{-}\Delta$ modulator and modulus control.                                                                                                                                                                                                                                                                                                                                                                                                                          | 111 |  |  |

| Figure 4.17 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |  |  |

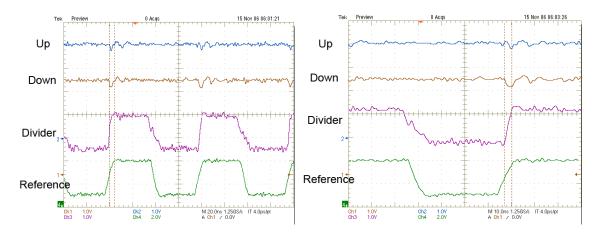

| Figure 4.18 | Measured input and output signals of the PFD in a locked loop.                                                                                                                                                                                                                                                                                                                                                                                                                                         | 114 |  |  |

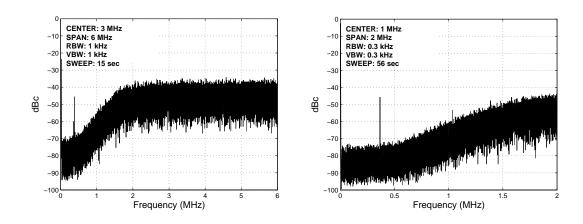

| Figure 4.19 | Measured noise shaping of the FPGA implemented $\Sigma\text{-}\Delta$ modulator.                                                                                                                                                                                                                                                                                                                                                                                                                       | 114 |  |  |

| Figure 4.20 | Measured output spectra of the frequency divider.                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 115 |  |  |

| Figure 4.21 | Measured spectra of the fractional- $\it N$ synthesiser with 10 MHz span (left) and 1 MHz span (right).                                                                                                                                                                                                                                                                                                                                                                                                | 115 |  |  |

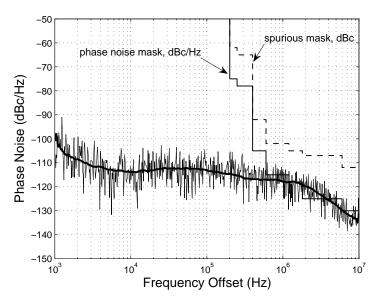

| Figure 4.22 | Measured phase noise of the fractional-N synthesiser.                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 116 |  |  |

| Figure 4.23 | Simulated quantisation noise contribution to the synthesiser.                                                                                                                                                                                                                                                                                                                                                                                                                                          | 116 |  |  |

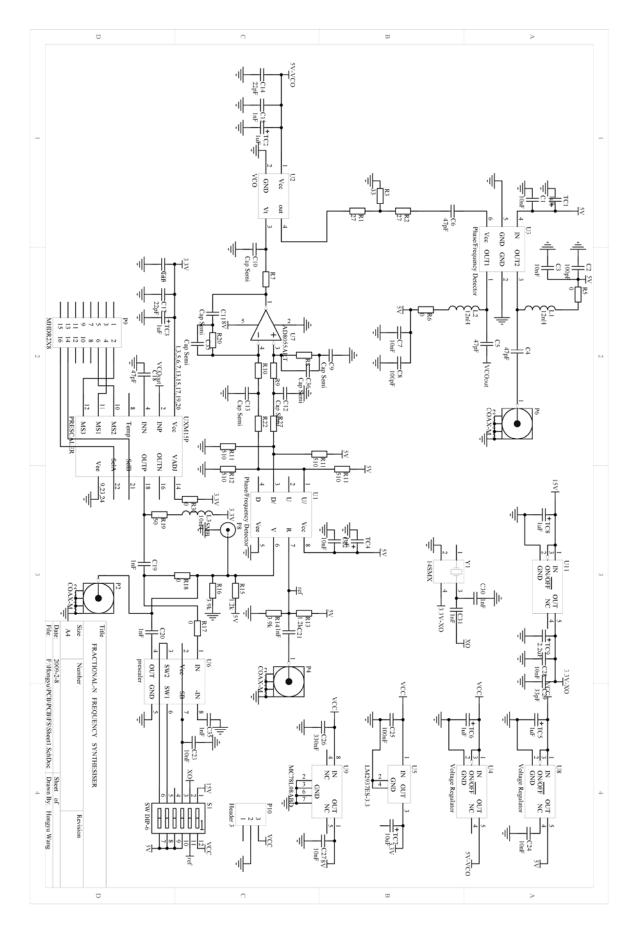

| Figure 4.24 | Circuit diagram of the implemented synthesiser.                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 117 |  |  |

| Figure 4.25 | RF section of the high reference frequency fractional-N synthesiser.                                                                                                                                                                                                                                                                                                                                                                                                                                   | 119 |  |  |

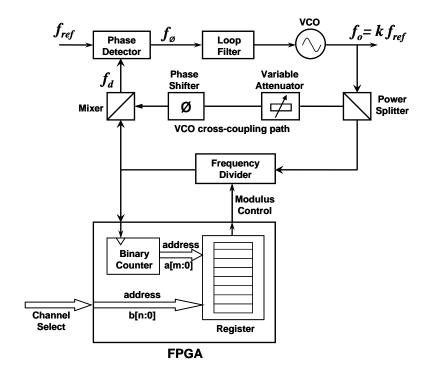

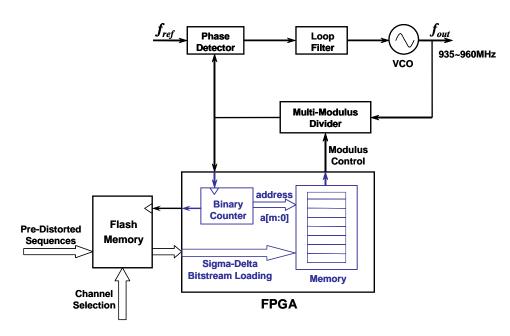

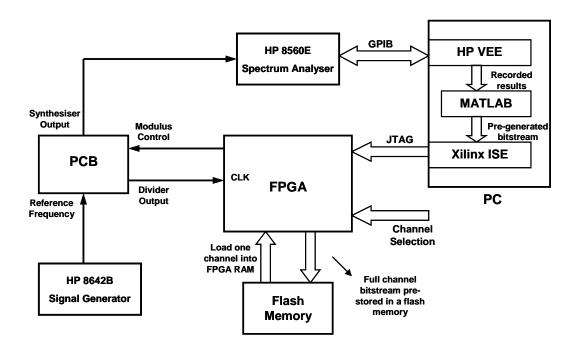

| Figure 4.26 | Block diagram of a stored-sequence fractional-N frequency synthesiser.                                                                                                                                                                                                                                                                                                                                                                                                                                 | 119 |  |  |

| Figure 4.27 | Experimental setup of the synthesiser measurement.                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 120 |  |  |

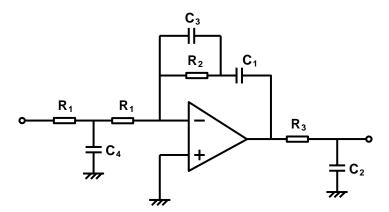

| Figure 4.28 | Enhanced loop filter design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 120 |  |  |

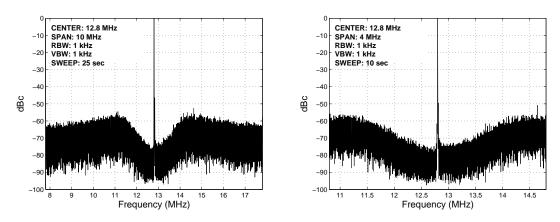

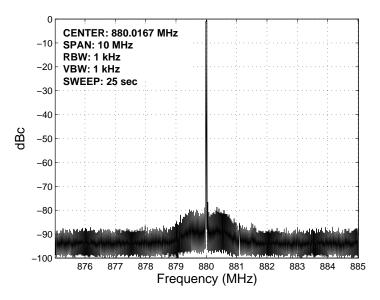

| Figure 4.29 | Measured spectrum of the synthesiser at integer mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 121 |  |  |

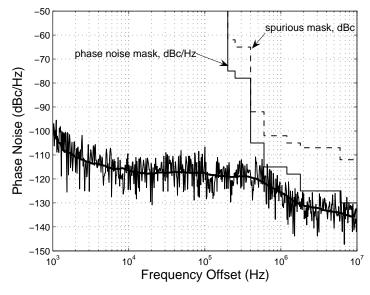

| Figure 4.30 | Measured phase noise of the synthesiser at integer mode.                                                                                                                                                                                                                                                                                                                                                                                                                                               | 123 |  |  |

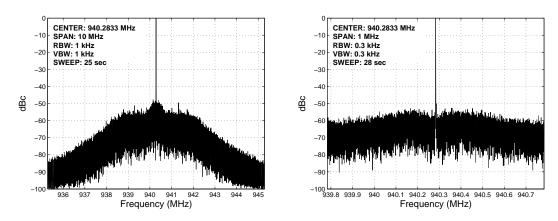

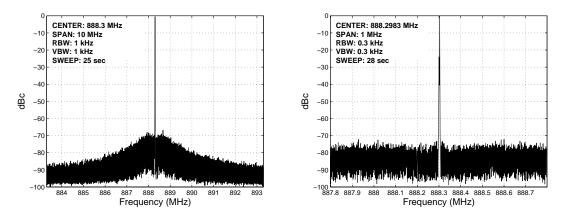

| Figure 4.31 | Measured fractional-N synthesiser output spectra.                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 124 |  |  |

| Figure 4.32 | Measured phase noise of the fractional-N frequency synthesiser.                                                                                                                                                                                                                                                                                                                                                                                                                                        | 124 |  |  |

| Figure 4.33 | Measured fractional-N synthesiser output spectra.                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 125 |  |  |

| Figure 4.34 | Measured phase noise of the fractional-N frequency synthesiser.                                                                                                                                                                                                                                                                                                                                                                                                                                        | 125 |  |  |

| Figure 5.1  | General form of a fractional- ${\it N}$ frequency synthesiser, showing a VCO cross-coupling path.                                                                                                                                                                                                                                                                                                                                                                                                      | 130 |  |  |

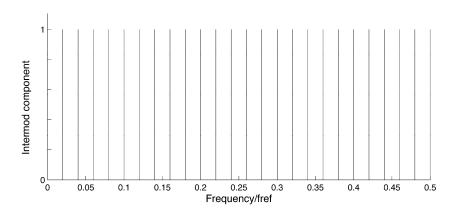

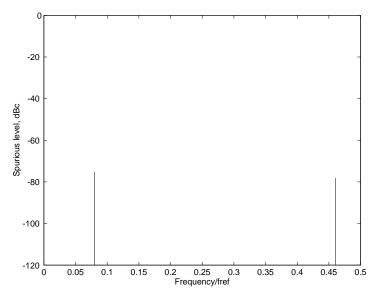

| Figure 5.2  | Potential components in a fractional- $N$ synthesiser due to VCO/reference frequency intermodulation, with 0.46 fractionality.                                                                                                                                                                                                                                                                                                                                                                         | 132 |  |  |

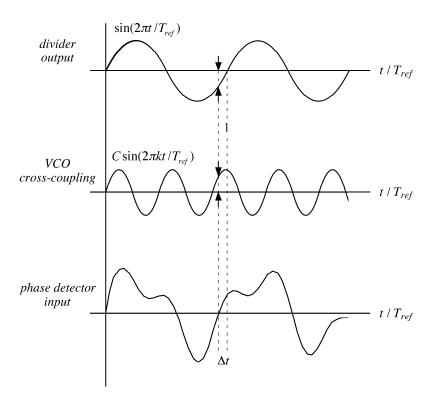

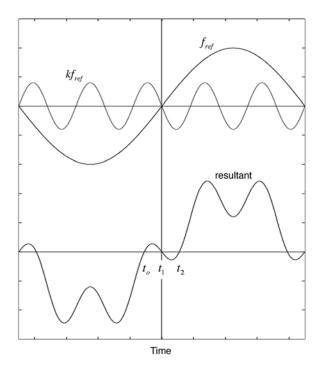

| Figure 5.3  | Illustration of the effect of VCO cross-coupling onto the phase detector input.                                                                                                                                                                                                                                                                                                                                                                                                                        | 134 |  |  |

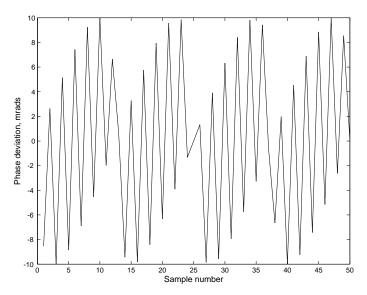

| Figure 5.4  | Modelled phase jitter resulting from -40 dB VCO cross-coupling with 90.46 divider ratio.                                                                                                                                                                                                                                                                                                                                                                                                               | 135 |  |  |

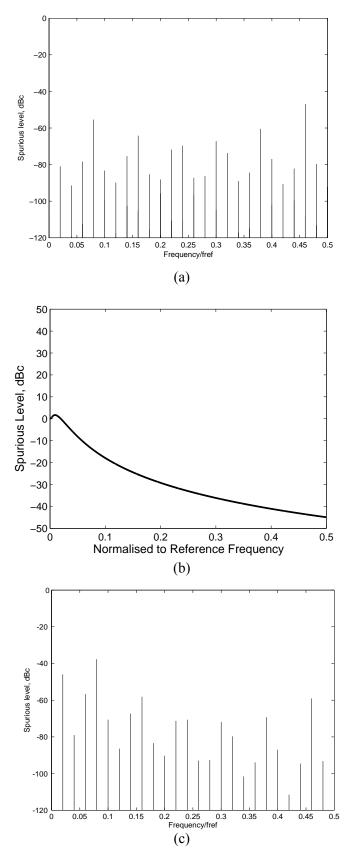

| Figure 5.5  | igure 5.5 Numerically-predicted spurious components due to -40 dB VCO-phase detector cross-coupling in a fractional-N synthesiser; output frequency = 1809.2 MHz, reference frequency = 20 MHz, loop natural frequency = 250 kHz. (a) Spur distribution at phase detector input. (b) PLL response. (c) Spur distribution at synthesiser output. |     |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

| Figure 5.6  | Numerically-predicted spurious components due to VCO-phase detector cross-coupling in a fractional- <i>N</i> synthesiser; output frequency = 1809.2 MHz, reference frequency = 20 MHz, loop natural frequency = 250 kHz, VCO cross-coupling = 60 dB.                                                                                            |     |  |  |  |

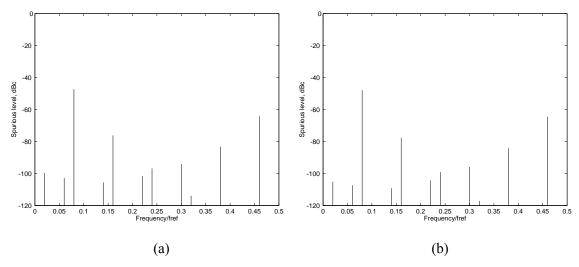

| Figure 5.7  | Comparison of analytic (a) and numerical (b) predicted spurious components due to VCO-phase detector cross-coupling in a fractional- <i>N</i> synthesiser; output frequency = 1809.2 MHz, reference frequency = 20 MHz, loop natural frequency = 250 kHz, VCO cross-coupling = -46 dB.                                                          |     |  |  |  |

| Figure 5.8  | Illustration of excessive VCO-to-phase detector cross-coupling leading to loop instability.                                                                                                                                                                                                                                                     | 142 |  |  |  |

| Figure 5.9  | Numerically-modelled VCO phase noise profile for a fractional- $N$ synthesiser, output frequency = 1809.2 MHz, reference frequency = 20 MHz, loop natural frequency = 250 kHz, no VCO cross-coupling.                                                                                                                                           | 144 |  |  |  |

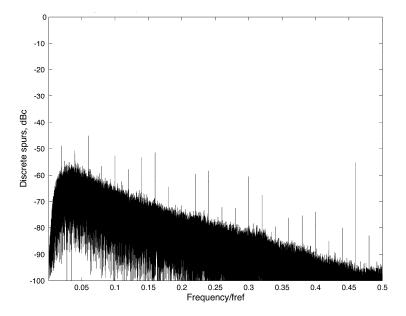

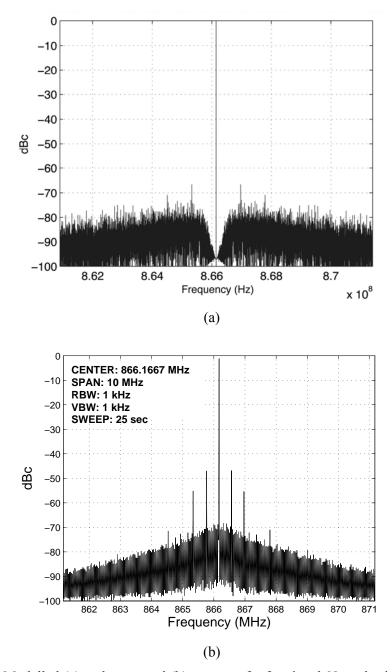

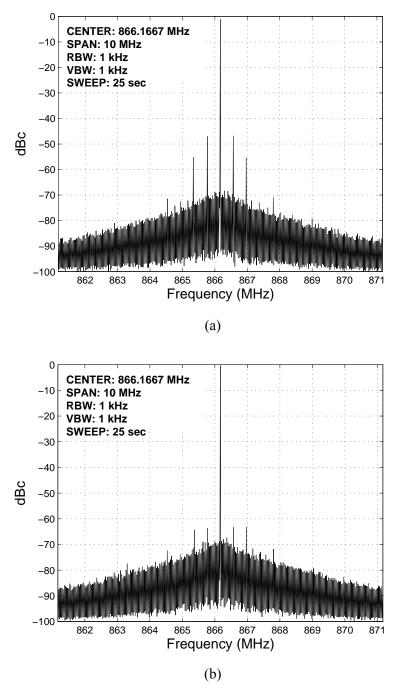

| Figure 5.10 | Modelled (a) and measured (b) spectra of a fractional- <i>N</i> synthesiser with 255/1024 fractionality, 105 MHz reference frequency and 250 kHz loop natural frequency; no external applied VCO cross-coupling.                                                                                                                                | 145 |  |  |  |

| Figure 5.11 | Modelled (a) and measured (b) spectra of a fractional- <i>N</i> synthesiser with 255/1024 fractionality, 105 MHz reference frequency and 250 kHz loop natural frequency; 20 dB external VCO cross-coupling.                                                                                                                                     | 146 |  |  |  |

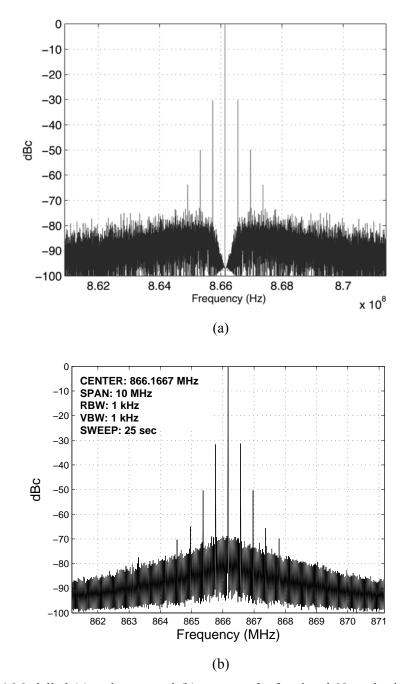

| Figure 5.12 | Modelled (a) and measured (b) spectra of a fractional- <i>N</i> synthesiser with 511/1024 fractionality, 105 MHz reference frequency and 250 kHz loop natural frequency; no external applied VCO cross-coupling.                                                                                                                                | 147 |  |  |  |

| Figure 5.13 | Modelled (a) and measured (b) spectra of a fractional- <i>N</i> synthesiser with 511/1024 fractionality, 105 MHz reference frequency and 250 kHz loop natural frequency; 19 dB external VCO cross-coupling.                                                                                                                                     | 148 |  |  |  |

| Figure 5.14 | The architecture of a fractional- ${\cal N}$ frequency synthesiser with phase compensation technique.                                                                                                                                                                                                                                           | 150 |  |  |  |

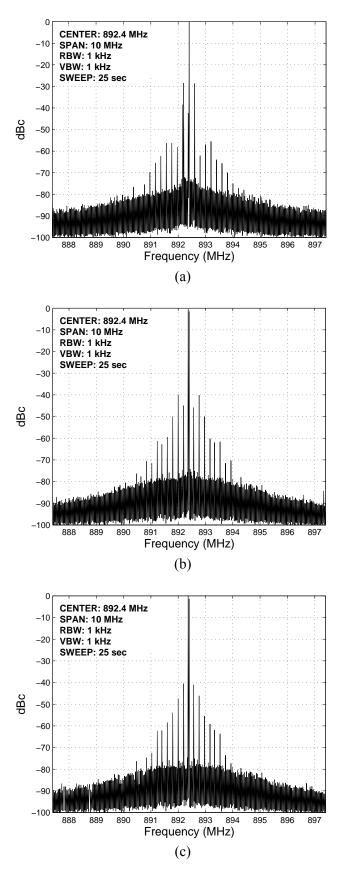

| Figure 5.15 | Measured spectrum of a fractional- $N$ synthesiser with 511/1024 fractionality, 105 MHz reference frequency and 250 kHz loop natural frequency. (a) No external applied cross-coupling. (b) Controlled amplitude (-23 dB) and phase cross-coupling. (c) -24 dB cross-coupling with 5° phase shift relative to the measurement in (b).           | 153 |  |  |  |

| Figure 5.16 | Measured spectrum of a fractional- <i>N</i> synthesiser with 255/1024 fractionality, 105 MHz reference frequency and 250 kHz loop natural frequency. (a) No external applied cross-coupling. (b) Controlled amplitude and phase cross-coupling.                                                                                                 | 154 |  |  |  |

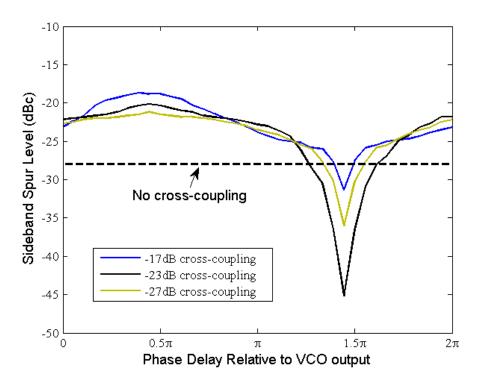

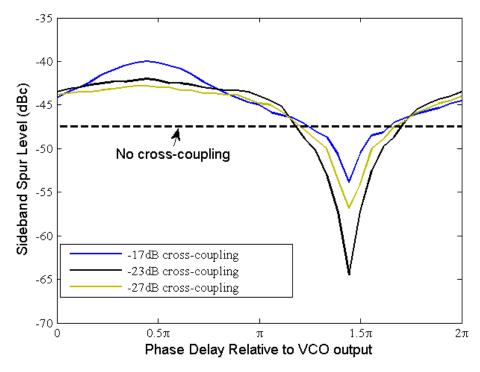

| Figure 5.17 | Measured sideband spur level versus a controlled amplitude and phase cross-coupling, with 511/1024 fractionality, 105 MHz reference frequency and 250 kHz loop natural frequency.                                                                                                                                                               | 155 |  |  |  |

| Figure 5.18 | Measured sideband spur level versus a controlled amplitude and phase cross-coupling, with 255/1024 fractionality, 105 MHz reference frequency and 250 kHz loop natural frequency.                                                                                                                                                               | 155 |  |  |  |

| Figure 6.1  | Proposed pre-distortion stored-sequence $\Sigma$ - $\Delta$ fractional- $N$ synthesiser.                                                                                                                                                                                                                                                        | 158 |  |  |  |

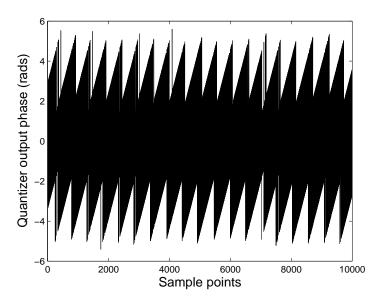

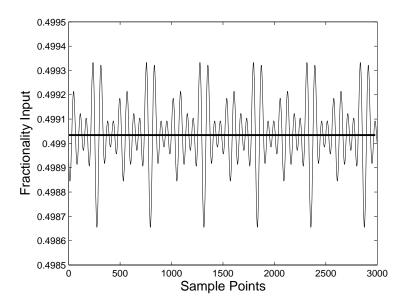

| Figure 6.2  | Modelled phase jitter of third-order single-bit $\Sigma\text{-}\Delta$ modulator with 511/1024 input.                                                                                                                                                                                                                                           | 161 |  |  |  |

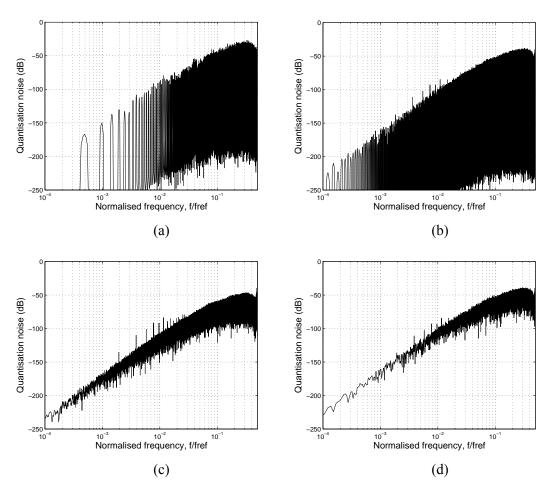

| Figure 6.3  | Modelled dithering effect of a third-order single-bit $\Sigma$ - $\Delta$ modulator with 511/1024 input. (a) No dithering. (b) LSB dithering of 1/2 <sup>14</sup> . (c) LSB dithering of 1/2 <sup>17</sup> . (d) Small pseudo-random noise dithering.                      |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Figure 6.4  | Input of a $\Sigma$ - $\Delta$ modulator with and without pre-distortion signals, fractionality = 16 511/1024.                                                                                                                                                             |  |  |  |

| Figure 6.5  | Experimental setup of the pre-distortion synthesiser measurement. 16                                                                                                                                                                                                       |  |  |  |

| Figure 6.6  | Modelled quantisation noise PSD of a $\Sigma$ - $\Delta$ modulator with 511/1024 fractionality, without (a) and with (b) the proposed pre-distortion technique.                                                                                                            |  |  |  |

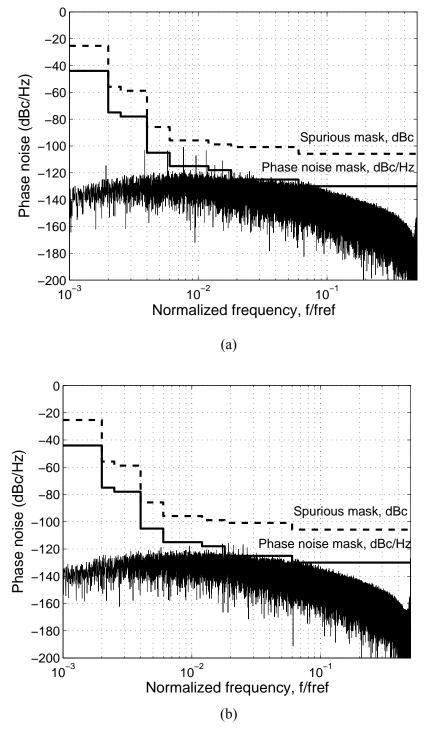

| Figure 6.7  | Modelled phase noise of a fractional- <i>N</i> synthesiser with 511/1024 fractionality, 100 kHz loop natural frequency, without (a) and with (b) proposed predistortion technique.                                                                                         |  |  |  |

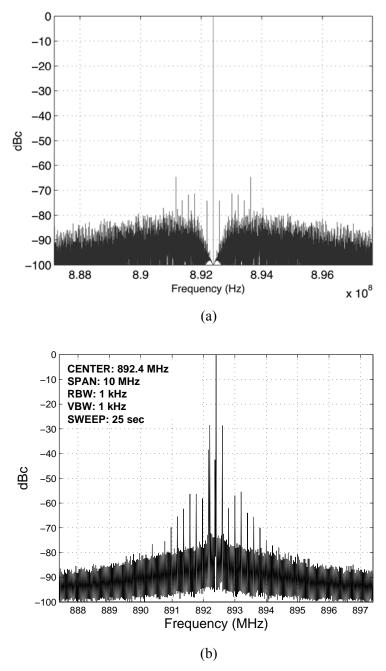

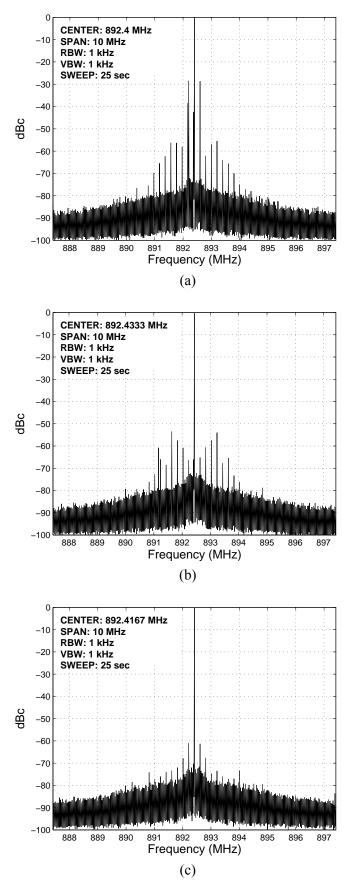

| Figure 6.8  | Measured spectra of a fractional- <i>N</i> synthesiser with 511/1024 fractionality, 105 MHz reference frequency and 250 kHz loop natural frequency. (a) No predistortion. (b) Pre-distortion on first pair of sideband spurs. (c) Pre-distortion on all of sideband spurs. |  |  |  |

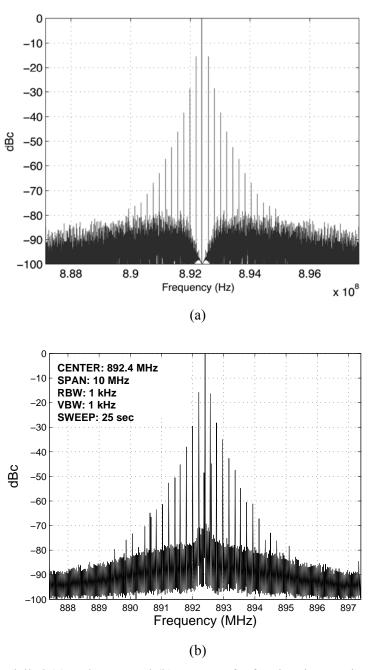

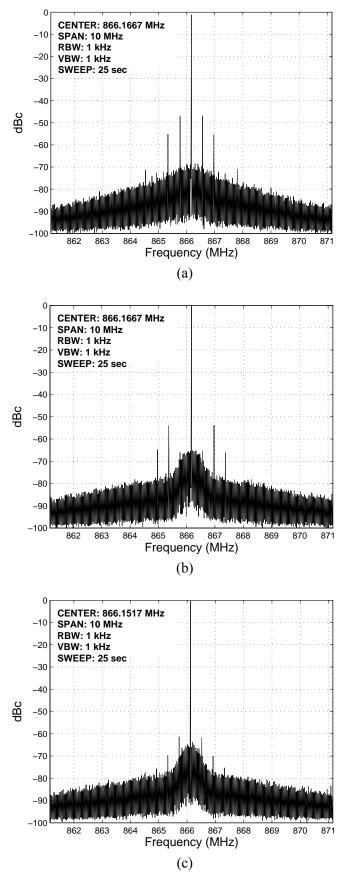

| Figure 6.9  | Measured spectra of a fractional- <i>N</i> synthesiser with 255/1024 fractionality, 105 MHz reference frequency and 250 kHz loop natural frequency. (a) No predistortion. (b) Pre-distortion on first pair of sideband spurs. (c) Pre-distortion on all of sideband spurs. |  |  |  |

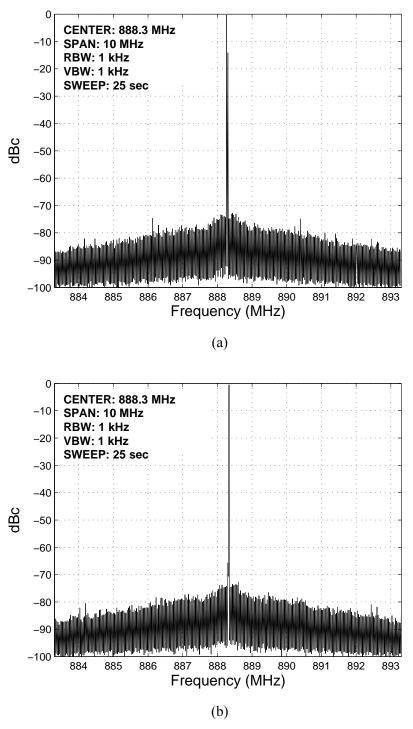

| Figure 6.10 | <ul> <li>Measured spectra of a fractional-N synthesiser with 471/1024 fractionality, 105 MHz reference frequency and 250 kHz loop natural frequency. (a) No predistortion signal. (b) Pre-distortion on sideband spurs.</li> </ul>                                         |  |  |  |

# **List of Principal Symbols**

| SYMBOL                         | DEFINITION                                        | UNIT  |

|--------------------------------|---------------------------------------------------|-------|

| $arDelta\phi$                  | Phase Error                                       | rad   |

| $arDelta\phi_{in}$             | Input phase jitter                                | rad   |

| $\Delta\omega_H$               | Hold-in limit                                     | rad/s |

| $\Delta\omega_L$               | Lock-in limit                                     | rad/s |

| $\Delta\omega_P$               | Pull-in limit                                     | rad/s |

| $\Delta t$                     | Timing jitter                                     | S     |

| $\Delta t_n$                   | Timing jitter                                     | S     |

| Φ                              | Phase                                             | Deg   |

| $\alpha$                       | Fractional part of division ratio                 | -     |

| $	heta_e$                      | Phase error                                       | rad   |

| $	heta_i$                      | Input phase                                       | rad   |

| $\phi$                         | Generic phase value                               | Deg   |

| $\tau_1$ , $\tau_2$ , $\tau_3$ | Generic loop filter time constants                | S     |

| $\omega$                       | Angular frequency                                 | rad/s |

| $\omega_c$                     | Cut-off frequency                                 | rad/s |

| $\omega_n$                     | Loop natural frequency                            | rad/s |

| $\omega_o$                     | Angular output frequency                          | rad/s |

| а                              | Generic phase term used in trigonometric identity | rad   |

| В                              | Bandwidth                                         | Hz    |

| $B_n$                          | Noise bandwidth                                   | Hz    |

| b                              | Generic phase term used in trigonometric identity | rad   |

| C(s)                           | Generic Laplace output signal                     | -     |

| $C_1$ , $C_2$ , $C_3$          | Loop filter capacitor values                      | F     |

| D                              | Division ratio                                    | -     |

| E(z)                           | Error signal introduced by quantizers             | -     |

| F                              | Noise factor                                      | -     |

| F(s)                           | Loop filter Laplace transfer function             | -     |

| f                              | Fourier frequency (sideband, offset, baseband)    | Hz    |

| $f_c$              | Cut-off frequency                                                      | Hz                   |

|--------------------|------------------------------------------------------------------------|----------------------|

| $f_d$              | PFD Frequency                                                          | Hz                   |

| $f_i$              | Input frequency                                                        | Hz                   |

| $f_o$              | Output frequency                                                       | Hz                   |

| $f_s$              | Sampling frequency                                                     | Hz                   |

| G(s)               | Open loop forward gain of PLL                                          | Rad/s                |

| H(s)               | Feedback gain                                                          | Rad/s                |

| K                  | Collective gain of all PLL frequency independent constants             | mA/V                 |

| $K_{VCO}$          | VCO gain                                                               | Hz/V                 |

| k                  | Boltzmann's constant, $(1.38 \times 10^{-23})$                         | J/K                  |

| $L(f_m)$           | Single side band phase noise at offset frequency $f_m$                 | dBc/Hz               |

| $L(\omega_m)$      | Single sideband signal to carrier ratio at offset frequency $\omega_m$ | dBc/Hz               |

| L                  | Binary word length                                                     | -                    |

| M                  | The binary equivalent of the DDS input word                            | -                    |

| m                  | Multiplier of radio frequency                                          | -                    |

| N                  | Generic n-divider division value                                       | -                    |

| n                  | Multiplier of local oscillator frequency                               | -                    |

| P                  | Dual modulus prescaler division value                                  | -                    |

| Q                  | Quality factor                                                         | -                    |

| $Q_i(\omega)$      | Quantisation noise power                                               | W                    |

| R                  | Generic R-divider value                                                | -                    |

| $R_1,R_2,R_3$      | Loop filter resistor values                                            | Ω                    |

| $S\phi_{in}(f_m)$  | Input double-sided spectral density of phase fluctuations              | rad <sup>2</sup> /Hz |

| $S\phi_{out}(f_m)$ | Output double-sided spectral density of phase fluctuations             | rad <sup>2</sup> /Hz |

| S                  | Laplace operator                                                       | -                    |

| ζ                  | Damping factor                                                         | -                    |

| T                  | Absolute temperature                                                   | K                    |

| $T_L$              | Lock-in time                                                           | S                    |

| $T_P$              | Pull-in time                                                           | S                    |

| $T_{ref}$          | Reference cycle period                                                 | S                    |

| $T_S$              | Sampling cycle period into phase frequency detector                    | S                    |

| t                  | Time                                                                   | S                    |

| v(s)               | Voltage signal, Laplace domain                                         | V                    |

| v(t)               | Voltage signal, time domain                                            | V                    |

#### List of Abbreviations

**SYMBOL DEFINITION**

3G Third Generation

3GPP 3<sup>rd</sup> Generation Partnership Project

ADC Analogue to Digital Converter

ADS Advanced Design System

AFC Automatic Frequency Control

AM Amplitude Modulation

CMOS Complementary Metal Oxide Semiconductor

CP Charge Pump

CPLD Complex Programmable Logic Device

DAC Digital to Analogue Converter

DC Direct Current

DCI Digital Controlled Impedance

DCS Digital Cellular System

DDFS Direct Digital Frequency Synthesiser

DDS Direct Digital Synthesis

EDGE Enhanced Data rates for GSM Evolution

FM Frequency Modulation

FOM Figure Of Merit

FPGA Field-Programmable Gate Array

FSK Frequency-Shift Keying

GPRS General Packet Radio Service

GSM Global System for Mobile communications, (formally known as

Groupe Speciale Mobile)

HSCSD High Speed Circuit Switched Data

IC Integrated Circuit

LO Local Oscillator

LSB Least Significant Bit

MMIC Monolithic Microwave Integrated Circuit

MSB Most Significant Bit

OCXO Oven Controlled Crystal Oscillator

PCB Printed Circuit Board

PECL Positive Emitter-Coupled Logic

PFD Phase Frequency Detector

PLL Phase Locked Loop

PM Phase Modulated

PSD Power Spectral Density, (single side-band phase noise)

ROM Read Only Memory

RF Radio Frequency

RMS Root Mean Square

SNR Signal to Noise Ratio

SSB Single Side-Band

TCXO Temperature Controlled Crystal Oscillator

TDMA Time Division Multiple Access

VCO Voltage Controlled Oscillator

WCDMA Wide-band Code Division Multiple Access

# **Chapter 1**

#### Introduction

#### 1.1 The Issue of Frequency Synthesis

Wireless personal communications have been growing inexorable due to ever emerging new applications and falling prices. The applications of wireless communication devices include cordless phones, cellular phones, global positioning systems, wireless local area networks and radio frequency identification devices, conveying voice, video and other kinds of data. Signal purity of these radio frequency systems determines the effective usability of the radio spectrum. The need for spectrally clean frequency sources has been an almost timeless pursuit for nearly the entire history of humanity. Common to all systems and standards competing for radio space are specifications defining the allowable amount of frequency drift and spurious emissions that each system can impact on its neighbours.

The Phase-Locked Loop (PLL) method of frequency synthesis is now the most commonly used for producing high frequency local oscillators in modern communications equipment. Most modern amateur or commercial transceivers employ at least one if not several, PLL systems, to generate stable high frequency oscillations. PLLs are widely used in a variety of applications, which include line synchronisation and colour sub-carrier recovery in TV receivers, synthesised local oscillators and FM demodulators in radio receivers and frequency synthesisers in transceivers and signal generators, to name but a few [1]. As an essential part of these applications, designers have been exploring new advanced PLL techniques about PLL system with lower noise and better performance.

Modern communication products, from TV sets to mobile phones, universally use a circuit known as a frequency synthesiser to generate a selected range of frequencies to allow the product to tune to different channels and frequencies. In many applications, particularly cellular communications, these synthesisers need to produce fairly pure

signals and simultaneously be able to switch between channels rapidly. Conventional integer-N synthesisers [2-4] are very difficult to satisfy the need of fine channel resolution, fast settling and low in-band noise simultaneously. More recently, a technique known as fractional-N synthesis, especially PLL based sigma-delta ( $\Sigma$ - $\Delta$ ) fractional-N synthesis [5-9] has been developed to satisfy this requirement of modern wireless communications.