# High-Performance Resistance Switching Memory Devices Using Spin-On Silicon Oxide

Wing H. Ng<sup>(D)</sup>, *Member, IEEE*, Adnan Mehonic, Mark Buckwell, Luca Montesi, and Anthony J. Kenyon<sup>(D)</sup>, *Senior Member, IEEE*

Abstract—In this paper, we present high-performance resistance switching memory devices (RRAM) with a SiO<sub>2</sub>-like active layer formed from spin-on hydrogen silsesquioxane (HSQ). Our metal– insulator-metal devices exhibit switching voltages of less than 1 V, cycling endurance of more than  $10^7$  cycles without failure, electroforming below 2 V at room temperature, and retention time of resistance states of more than  $10^4$  seconds at temperatures up to 120 °C. We also report arrays of nanoscale HSQ-based RRAM devices in the form of multilayer nanopillars with switching performance comparable to that of our thin film devices. We are able to address and program individual RRAM nanopillars using conductive atomic force microscopy. These promising results, coupled with a much easier fabrication method than traditional ultrahigh vacuum-based deposition techniques, make HSQ a strong candidate material for the next-generation memory devices.

*Index Terms*—Analog memory, atomic force microscopy, dielectric films, nanofabrication, resistive RAM, silicon compounds.

## I. INTRODUCTION

**R** ESISTANCE switching random access memory (RRAM) has attracted a lot of effective in has attracted a lot of attention in recent years due to its excellent electronic properties, such as nanosecond switching time [1], high degree of scalability and low operating voltages [2]. These qualities make RRAM a good candidate for the next generation of memory devices as conventional NAND Flash technology reaches the end of the roadmap and as new classes of so-called storage class memory are developed. There have been numerous reports in the literature of materials that exhibit resistance switching, the most extensively studied of which include transition metal oxides such as  $HfO_2$  [3],  $TiO_2$ [4], and TaO<sub>2-x</sub> [5]. Recently, however, silicon oxide (SiO<sub>x</sub>) has also demonstrated excellent resistance switching performance [6]–[8]. The main advantages of using  $SiO_x$  are two-fold: first, the material is very abundant and readily available; second, it is fully compatible with CMOS manufacturing processes and materials. The most common methods for depositing  $SiO_x$  as

The authors are with the Department of Electronic and Electrical Engineering, University College London, London WC1E 7JE, U.K. (e-mail: w.ng@ucl.ac.uk; adnan.mehonic.09@ucl.ac.uk; mark.buckwell.11@ucl.ac.uk; luca.montesi.13@ucl.ac.uk; a.kenyon@ucl.ac.uk).

Digital Object Identifier 10.1109/TNANO.2017.2789019

thin film materials are sputtering, Chemical Vapour Deposition (CVD) and Atomic Layer Deposition (ALD). While these techniques are well established and the layer thicknesses are extremely controllable, they require deposition in a high vacuum environment and are multi-step processes. In this paper, we propose using a spin-on  $SiO_2$ -like hydrogen silsesquioxane (HSQ) as the active switching material, and we demonstrate fabrication of high performance non-volatile micro- and nanoscale RRAM devices using this material.

The main advantage of using HSQ from a fabrication prospective is that it can be applied onto most metallic and semiconductor surfaces by spin-coating alone at ambient conditions, hence it simplifies the fabrication process. The layer thickness can be controlled precisely by a combination of solution concentration, spin speed and spin duration. While there have been several previous reports of using HSQ in RRAM devices, the HSQ layer used in these reported works were doped with either nanoparticles or metal ions [9]. Our work is distinctively different from these previous reports as we demonstrate switching that is intrinsic to the HSQ thin film; no metal doping is required.

### II. HYDROGEN SILSESQUIOXANE

Since its discovery in the 1970s [10], HSQ has been commonly used in the semiconductor industry as a spin-on insulator for microelectronic devices due to its excellent planarisation performance and gap-filling properties. In the 1990s, Namatsu *et al.*, demonstrated that HSQ can be used as a negative tone resist for electron beam lithography [11], with feature sizes of the order of a few nanometres patterned routinely [12], [13].

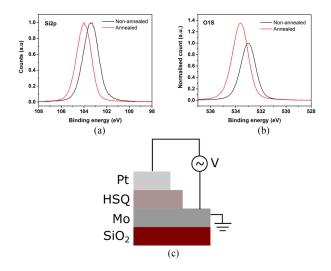

The HSQ molecule has a cage structure which consists of silicon, oxygen, and hydrogen networks, and has a general formula of  $(HSiO_{3/2})_{2n}$ . Upon spin-coating and annealing, these cage structures open up and cross-link to form a networked structure of amorphous silicon oxide [14]. We performed X-ray Photoelectron Spectroscopy (XPS) scans on two spin-coated HSQ thin films on Si substrates to demonstrate the effect of thermal annealing. The XPS spectra were taken a few nanometres below the surface to ensure we measured the bulk material rather than the surface. Fig. 1(a) shows the XPS spectra in the range corresponding to the Si2p region; spectra were normalised to the same intensity. The Si2p peak for the sample annealed at 160 °C for 2 minutes shifts to a higher energy (104 eV) compared to that of the non-annealed sample, indicating that the crosslinked (annealed) film is more SiO<sub>2</sub>-like compared

This work is licensed under a Creative Commons Attribution 3.0 License. For more information, see http://creativecommons.org/licenses/by/3.0/

Manuscript received July 30, 2017; revised November 29, 2017; accepted December 21, 2017. Date of publication January 26, 2018; date of current version September 6, 2018. This work was supported in part by the Engineering and Physical Sciences Research Council, U.K., under Grant EP/K01739X/1, and in part by the Leverhulme Trust under Grant RPG-2016-135. The review of this paper was arranged by the MEMRISYS 2017 Guest Editors. (*Corresponding author: Wing H. Ng.*)

Fig. 1. HSQ thin film XPS spectra and MIM device schematic. (a) Normalised XPS spectra for the non-annealed and annealed HSQ film on Si substrate in the Si2p peak region. (b) XPS depth profile spectra for the same non-annealed and annealed HSQ film in the O1s region. These spectra were normalised to the Si peak at 99 eV. (c) Cross-section schematic of our HSQ based MIM RRAM device.

to the non-crosslinked (un-annealed) film. The XPS spectra for the same samples in the O1s region [see Fig. 1(b)] shows a binding energy shift to higher energy for the annealed film. The O1s spectra were normalised to the Si peak at 99 eV, and by analysing the area under each peak, we were able to estimate the oxygen content in the annealed (crosslinked) HSQ film to be around 40% higher than in the non-annealed film.

## III. HSQ THIN FILM RRAM DEVICES

After establishing that the annealed HSQ film is SiO<sub>2</sub>-like, we fabricated our RRAM devices in a two-terminal metal-insulatormetal (MIM) configuration. Fig. 1(c) is the schematic of the device structure. Devices were fabricated on a Si chip with a thermally grown SiO<sub>2</sub> layer on top to electrically insulate the bottom electrode of the device from the Si substrate. First, 200 nm of Mo was deposited onto the SiO<sub>2</sub> surface by sputtering to serve as the bottom electrode. A 35 nm thick HSQ layer was then spin-coated on top of the Mo and annealed at 160 °C for 2 minutes. A top Pt electrode was deposited by electron beam evaporation, the size of individual devices defined using a shadow mask with device sizes ranging from 200  $\mu$ m × 200  $\mu$ m.

Current-voltage (IV) measurements were preformed using a Keithley 4200 Semiconductor Characterisation System, a Signatone probe station and tungsten probes.

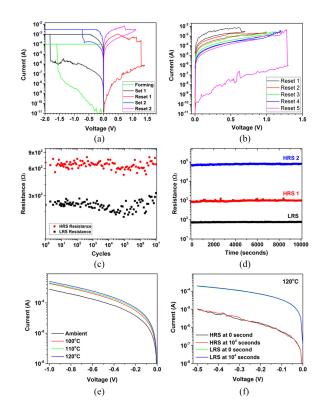

Fig. 2(a) shows typical current-voltage (IV) characteristics of our Mo-HSQ-Pt RRAM devices. We were able to electroform the devices at voltages as low as -1.6 V. Subsequently we could tailor the low resistance state (LRS) and high resistance state (HRS) through a combination of applied bias and current compliance. For example, after setting the device to the LRS at -1.8 V with a current compliance of 1 mA, we could reset the device with +1.3 V to the HRS [Set 1 and Reset 1 in Fig. 2(a)]. This gave us over 4 orders of magnitude of contrast between

Fig. 2. Current-Voltage, cycling and retention performance of our Mo-HSQ-Pt thin film RRAM devices. (a) Current-Voltage (IV) sweep for our Mo-HSQ-Pt RRAM devices showing forming and two sets of set/reset cycles to demonstrate controllable set and reset resistance levels. (b) Gradual reset of the RRAM device with increasing reset voltage. (c) Cycling performing between LRS and HRS states showing our devices is capable of more than  $10^7$  switching cycles. (d) Retention performance of 3 different resistance states of our device (Read voltage 0.2 V). (e) Temperature dependent IV characteristics of the LRS. (f) IV characteristics of the LRS and HRS at 120 °C at 0 seconds (first reading after the temperature has been stabilised) and  $10^4$  seconds. Demonstrating the state retention at high temperature.

the LRS and HRS. Note, a stronger reset process, achieved by sweeping the device to the higher positive voltages, results in higher set voltages, which could be in some cases greater than the initial electroforming voltage. Furthermore, the large drop in current for high reset voltage suggested that the device could be reset to a (near) pristine state, indicating that almost total destruction of the conductive path in the HSQ layer. However, we could lower the set and reset voltages to -0.7 V and +1.1 V, respectively, by adjusting the compliance current and still obtain over one order of magnitude contrast between LRS and HRS [Set 2 and Reset 2 in Fig. 2(a)]. Fig. 2(b) shows multiple resistance states, which we could programme by performing gradual resets (gradually increasing the reset voltage). These results demonstrate that our HSQ RRAM devices are potentially capable of multilevel bipolar switching.

We fitted the IV curves with a number of possible current transport mechanisms – trap assisted tunnelling, Fowler-Nordheim tunnelling, Poole-Frenkel hopping and thermionic (Schottky) emission. We found that the dominant transport mechanisms in our HSQ RRAM devices is trap assisted tunnelling, which is consistent with our previous reports of SiO<sub>x</sub> RRAM [2]. We performed temperature dependent IV measurements for our devices [see Fig. 2(e)] and our results showed that as we increase the device temperature, the LRS resistance decreases. This suggests that the switching mechanism is likely to be filamentary. We also observed no device size dependence of LRS current and this also indicates filamentary switching. These observations are consistent with our previous reports on SiO<sub>x</sub> based devices [15]. We are able to electroform and set our devices under negative bias (i.e., negative bias applied to top electrode), which indicates that mobile oxygen ions are pushed towards the bottom electrode (Mo) during the set process, leaving a silicon-rich channel behind. The subsequent reset under positive bias reintroduces the oxygen ions into the system, leaving the system in a higher resistance state [16].

Apart from changes in the bulk HSQ layer, chemical and structural changes at the insulator-metal (HSQ-Mo) interface under applied bias could also contribute to the switching mechanism. We are planning further work to investigate interfacial changes such as proton exchange [17], [18] and the formation of molybdenum oxide [19], [20] at the interface in order to gain a deeper understanding of the switching mechanisms in our devices.

Our HSQ-based RRAM devices showed excellent cycling performance as shown in Fig. 2(c), achieving more than  $10^7$ switching cycles. Note that the contrast between the two resistance states during the endurance test is lower than that shown in Fig. 2(a). This is because we used short and low-amplitude pulses for the endurance test (set pulse: -1.05 V, 150 ns; reset pulse: +1.1 V, 5  $\mu$ s) to prevent significant current overshoots, as we did not use controller transistors in our set-up. We anticipate that the integration of controller transistors would allow us to use higher voltage pulses that would increase the resistance state contrast while preventing hard breakdown of devices. We have performed retention measurements for multiple resistance states at room temperature [see Fig. 2(d)], and at 120 °C [see Fig. 2(f)]; our devices showed excellent retention performance – up to  $10^4$  seconds at both ambient and elevated temperatures. These IV, cycling and retention characteristics are comparable with those we have previously reported for sputtered silicon oxide based RRAM [21].

## IV. HSQ RRAM NANOPILLARS

From a technological point of view, it is important to shrink the individual device size to the nanoscale in order to achieve high density memory modules. In order to show that our devices work in the nanoscale regime, we fabricated MIM devices in the form of nanopillar arrays by single shot electron beam lithography. We have demonstrated in our previous work that we could fabricate nanoarrays over millimetre areas within only a few hours using this technique [22]. The HSQ nanopillar devices were fabricated on a Si wafer with a 4  $\mu$ m thermal oxide layer, on top of which was 150 nm of Mo, which served as the bottom device electrode. The HSQ active switching layer and Ti/Au top contact were patterned using electron beam lithography and reactive ion etching (RIE).

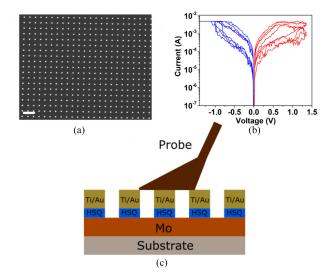

Fig. 3. HSQ nanopillar RRAM array. (a) Scanning electron microscope image of the nanopillar RRAM array showing excellent uniformity. Scale bar 3  $\mu$ m. (b) Current-voltage (IV) sweeps of our Mo-HSQ-Au RRAM nanopillar array showing multiple set and reset cycles. (c) schematic of the probe needle probing the IV of a group of nanopillars.

Fig. 3(a) shows a scanning electron microscope (SEM) plan view image of a section of the nanopillar RRAM sample. The nanopillars are 150 nm high (35 nm of HSQ plus 115 nm of Ti/Au), 300 nm in diameter and their spacing is 2  $\mu$ m. The sample has excellent uniformity in individual pillar size and inter-pillar spacing.

Fig. 3(b) shows IV sweeps of an HSQ nanopillar array using a probe needle to make contact. The schematic of the measurement set-up is shown in Fig. 3(c). Because the needle probe tip was much larger than an individual nanopillar, we were probing several nanopillars at once, and the switching process might involve more than one nanopillar. Nevertheless, the voltages required to set and reset are comparable to those of our MIM thin film devices (in the region of 1 V). We may also cycle the pillars many times between the LRS and HRS with over 1 order of magnitude of resistance contrast.

We probed the electrical characteristics of individual RRAM nanopillars by conductive atomic force microscopy (CAFM), landing a conductive probe on top of single pillars to measure their IV characteristics. In our preliminary work, we found that metal-coated silicon probes were too prone to wear on the rough, pillared surface; we therefore used boron-doped diamond probes on nickel cantilevers. These have a relatively high impedance of  $10^5$  to  $10^6 \Omega$  and a large radius of curvature, typically between 50–100 nm.

It is important to note that in our previous work we have made the diameter of the nanopillar of the order of tens of nanometres. However, devices of this size were unstable when addressed with diamond probes, due to the hardness of the diamond compared to the softness of the top electrode. Therefore, larger lateral size devices were fabricated for this work so that the contact between the probe tip and the pillar could be made more stable. For all measurements, the CAFM probe was grounded and the bias voltage was applied to the stage.

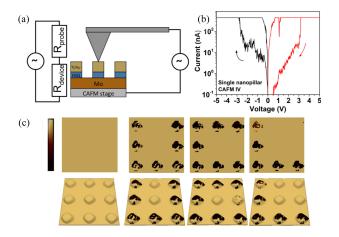

Fig. 4. Addressing individual HSQ RRAM nanopillars. (a) Schematic diagram showing the addressing of individual RRAM nanopillars (300 nm in diameter and 150 nm in height) using conductive atomic force microscopy (CAFM) technique. (b) IV sweep of an individual nanopillar, showing the set and reset cycle. (c) Demonstration of programming a  $3 \times 3$  nanopillar array by addressing each pillar individually. Top: 2D conductivity map of the CAFM scan over a  $3 \times 3$  nanopillar array. The far left one represents pristine state. By addressing individual nanopillars (i.e., either switching the pillar on or off), we can form the letter "U", "C" and "L" in sequence on the same array. Darker colour represents higher negative current. Bottom: 3D topography scan in contact mode after addressing the array and overlaying the image with the CAFM one. This shows there is no deformation of pillars after addressing the array. The top and bottom limits (lighter and darker colours) of the scale bar is -2 pA and -3 pA respectively.

An example of the IV sweeps using the CAFM on an individual nanopillar is shown in Fig. 4(b). The voltage applied to form the device is in the region of -2.8 V, and a subsequent read voltage of 0.5 V was applied, which showed that the device stayed in the LRS. We were able to reset the device in the opposite polarity at around +3.1 V, demonstrating bipolar switching. Note, the voltages required to form (and set) and reset are higher than those demonstrated in the thin film devices. However, this may be due to the impedance mismatch between the device and the CAFM instrumentation and/or poor contact between the nanopillar and probe tip.

In order to demonstrate that we could address multiple individual pillars to demonstrate programming capability, we used a  $3 \times 3$  pillar array onto which write letters of our choice. For each write/erase operation, the CAFM probe was lifted, positioned above the required nanopillar and then brought into close contact with the top electrode, meaning that there was no tunnelling gap. When reading the  $3 \times 3$  array, the probe was lifted from close contact to prevent wear of the pillars. This reduced the measured currents and made them somewhat variable (ranging from 5 pA to 12 nA with a mean of 2 nA and standard deviation of 4 nA) and increased the effective noise level. Current maps were therefore thresholded from -2 pA to remove the noise floor and cut off at -3 pA to best distinguish the state of each device in a binary manner (i.e., all current levels below -2 pArepresent "off" and the pillar is "switched on" for current levels above -3 pA). Fig. 4(c) shows a CAFM image of the  $3 \times 3$  pillar area scanned with 0.5 V bias to show all pillars were initially in the HRS (off state). Subsequently, we wrote the letters "U", "C" and "L" in the same array using form and reset operations to switch on and off individual nanopillars. This demonstrates that we are able to programme individual nanopillars to write an area using CAFM.

### V. CONCLUSION

In summary, we have demonstrated that HSQ is an excellent material for resistance switching applications. We can achieve bipolar intrinsic resistance switching by controlling the thin film thickness in our MIM devices. We could achieve one magnitude of LRS and HRS contrast with set and reset voltages of 1 V or less. Higher state contrast can easily be achieved with set and reset voltages of less than 2 V. The switching voltages are typically less than 1 V, with excellent cycling (>10<sup>7</sup> cycles) and retention performance (10<sup>4</sup> seconds) at temperatures up to 120 °C. One of the advantages of HSQ is ease of fabrication and processing compared with traditional UHV based techniques, such as sputtering and atomic layer deposition. We have demonstrated that highly uniform nanoscale RRAM arrays could be fabricated by single shot electron beam lithography, and we can address and programme individual nanopillars using CAFM.

### REFERENCES

- A. C. Torrezan, J. P. Strachan, G. Medeiros-Ribeiro, and R. S. Williams, "Sub-nanosecond switching of a tantalum oxide memristor," *Nanotechnology*, vol. 22, no. 48, Nov. 2011, Art. no. 485203.

- [2] A. Mehonic et al., "Resistive switching in silicon suboxide films," J. Appl. Phys., vol. 111, Apr. 2012, Art. no. 074507.

- [3] Y. S. Chen et al., "Highly scalable hafnium oxide memory with improvements," in Proc. 2009 IEEE Int. Electron Devices Meeting, Baltimore, MD, USA, 2009, pp. 1–4.

- [4] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," *Nature*, vol. 453, pp. 80–83, May 2008.

- [5] M.-J. Lee *et al.*, "A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta<sub>2</sub>O<sub>5-x</sub>/TaO<sub>2-x</sub> bilayer structures," *Nature Mater.*, vol. 10, pp. 625–630, Jul. 2011.

- [6] A. Mehonic *et al.*, "Electrically tailored resistance switching in silicon oxide," *Nanotechnology*, vol. 22, Oct. 2012, Art. no. 455201.

- [7] A. Mehonic *et al.*, "Structural changes and conductance thresholds in metal-free intrinsic SiO<sub>x</sub> resistive random access memory," *J. Appl. Phys.*, vol. 117, Mar. 2015, Art. no. 124505.

- [8] C. Li et al., "Three-dimensional crossbar arrays of self-rectifying Si/SiO2/Si memristors," *Nature Commun.*, vol. 8, Jun. 2017, Art. no. 15666.

- [9] Z. P. Rice, B. D. Briggs, S. M. Bishop, and N. C. Cady, "Development of a silicon oxide-based resistive memory device using a spin-on hydrogen silsesquioxane precursor," *J. Mater. Res.*, vol. 27, no. 24, pp. 3110–3116, Dec. 2012.

- [10] C. L. Frye and W. T. Collins, "Oligomeric silsesquioxanes (HSiO<sub>3/2</sub>)<sub>n</sub>," J. Amer. Chem. Soc., vol. 92, pp. 5586–5588, Sep. 1970.

- [11] H. Namatsu, Y. Takahashi, K. Yamazaki, T. Yamaguchi, M. Nagase, and K. Kurihara, "Three-dimensional siloxane resist for the formation of nanopatterns with minimum linewidth fluctuation," *J. Vac. Sci. Technol. B*, vol. 16, no. 1, pp. 69–76, Jan. 1998.

- [12] A. E. Grigorescu and C. W. Hagen, "Resists for sub-20-nm electron beam lithography with a focus on HSQ: State of the art," *Nanotechnology*, vol. 20, Jul. 2009, Art. no. 292001.

- [13] W. H. Ng *et al.*, "Design and fabrication of suspended indium phosphide waveguides for MEMS-actuated optical buffering," *IEEE J. Select. Topics Quantum Electron.*, vol. 21, no. 4, Jul./Aug. 2015, Art. no. 4400107.

- [14] A. G. Caster, S. Kowarik, A. M. Schwartzberg, O. Nicolet, S.-H. Limc, and S. R. Leone, "Observing hydrogen silsesquioxane cross-linking with broadband CARS," *J. Raman Spectrosc.*, vol. 40, pp. 770–774, 2009.

- [15] M. Buckwell, L. Montesi, S. Hudziak, A. Mehonic, and A. J. Kenyon, "Conductance tomography of conductive filaments in intrinsic siliconrich silica RRAM," *Nanoscale*, vol. 7, pp. 18030–18035, 2015.

- [16] J. J. Yang *et al.*, "The mechanism of electroforming of metal oxide memristive switches," *Nanotechology*, vol. 20, no. 21, May 2009, Art. no. 215201.

- [17] Y.-F. Chang, B. Fowler, Y.-C. Chen, and J. C. Lee, "Proton exchange reactions in SiO<sub>x</sub> -based resistive switching memory: Review and insights from impedance spectroscopy," *Prog. Solid State Chem.*, vol. 44, pp. 75– 85, Sep. 2016.

- [18] F. Zhou *et al.*, "A study of the interfacial resistive switching mechanism by proton exchange reactions on the SiOx layer," *Phys. Chem. Chem. Phys.*, vol. 18, pp. 700–703, Nov. 2015.

- [19] Y.-T. Chen *et al.*, "Influence of molybdenum doping on the switching characteristic in silicon oxide-based resistive switching memory," *Appl. Phys. Lett.*, vol. 102, Feb. 2013, Art. no. 043508.

- [20] Y. Ogawa, S. Shindo, Y. Sutou, and J. Koike, "Molybdenum oxide-base phase change resistive switching material," *Appl. Phys. Lett.*, vol. 111, Oct. 2017, Art. no. 163105.

- [21] A. Mehonic *et al.*, "Intrinsic resistance switching in amorphous silicon oxide for high performance SiOx ReRAM devices," *Microelectron. Eng.*, vol. 178, pp. 98–103, May 2017.

- [22] W. H. Ng and A. J. Kenyon, "Fabrication of large area nano-pillar arrays using a novel fast electron beam lithography technique," presented at the 2015 Mater. Res. Soc. Fall Meeting, Boston, MA, USA, Nov./Dec. 2015.

[Online]. Available: http://www.mrs.org/fall2015/program-session?code = p

**Wing H. Ng** (M'15) received the M.Sci. degree in physics from the University of Durham, Durham, U.K., in 2001, the M.Sc. degree in optics and photonics from Imperial College London, London, U.K., in 2002, and the Ph.D. degree in semiconductor physics from the University of Sheffield, Sheffield, U.K., in 2007.

He worked in the photonics industry for a number of years after receiving the Ph.D. degree. In 2013, he joined the Department of Electronic and Electrical Engineering, University College London, London,

U.K., where he is currently a Research Associate. His research interests include nanofabrication of semiconductor structures, microelectromechanical devices, optoelectronic devices, photonic integrated circuits, and resistive switching in SiO<sub>2</sub>- and polymer-based materials.

Dr. Ng is a Member of the Institution of Engineering and Technology (U.K.) and the Institute of Physics (U.K.).

Adnan Mehonic received the Graduate degree in electrical and electronic engineering from the University of Sarajevo, Sarajevo, Bosnia, in 2009, and the M.Sc. and Ph.D. degrees in nanotechnology and electronic engineering from the University College London, London, U.K., in 2010 and 2014, respectively.

Currently, he is working as a Research Fellow with the University College London. His current research interests include the study of thin oxide films and their applications in the field of novel nonvolatile memo-

ries and neuromorphic architectures. He is a recipient of the Royal Academy of Engineering Research Fellowship.

**Mark Buckwell** received the Bachelor's degree in medical physics and the Master's degree in nanotechnology from the University College London, London, U.K., in 2009 and 2013, respectively, focusing on neural stimulation and the functionalization of nanodiamonds for use in healthcare. Since 2013, he has been working toward the Doctorate degree, specializing in the characterization of dielectric materials for use in next-generation technologies. Between 2009 and 2015, he also worked as a Research Technician with the Neuro-otology Department, Imperial Col-

lege London, and Hammersmith Medicines Research, London, U.K., specializing in clinical research into human mobility and pharmaceuticals, respectively.

**Luca Montesi** received the B.Eng. (electrical) degree and the M.Eng. (electrical-thesis) degree from McGill University, Montreal, QC, Canada, 2009 and 2012, respectively. He is currently working toward the Ph.D. degree in electrical engineering at the University College London, London, U.K. He is focusing on filamentary  $SiO_x$ -based resistive RAM devices and, in particular, he is looking at novel electrical programming approaches as well as the role of emitted and absorbed oxygen.

Anthony J. Kenyon (M'08–SM'14) received the B.Sc. and D.Phil. degrees in chemical physics from the University of Sussex, Brighton, U.K., in 1986 and 1992, respectively.

In 1992, he joined the Electronic and Electrical Engineering Department, University College London, London, U.K., where he currently holds the position of a Professor of nanoelectronic and nanophotonic materials and the Vice Dean (Research). He is the Author of more than 90 peer-reviewed publications, and is on the editorial board of several journals. He reg-

ularly gives invited talks at major international meetings, and has co-organized a number of international symposia. His research interests include resistance switching, nanostructured materials for electronics and photonics; silicon photonics; neuromorphic devices, and self-assembled nanoscale systems.

Prof. Kenyon is a Fellow of both the Institute of Physics and the Institution of Engineering and Technology, and serves on the Executive Committee of the European Materials Research Society.