# REALISATION OF PARALLEL (P,Q) COUNTERS FOR HIGH-SPEED ARRAY MULTIPLIERS

BY

### **BAKRI MADON**

# DEPARTMENT OF ELECTRONIC AND ELECTRICAL ENGINEERING UNIVERSITY COLLEGE LONDON

Submitted in accordance with the requirements for the degree of

Doctor of Philosophy

September 1989

ProQuest Number: 10797676

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest 10797676

Published by ProQuest LLC (2018). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code

Microform Edition © ProQuest LLC.

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

#### **ACKNOWLEDGEMENTS**

I would like to express my appreciation to the many people who have made this work possible. First, and foremost, my sincere gratitude to my supervisor, Mr. Chris Guy for his patient guidance and continued encouragement throughout the production of this work. Also for his most helpful criticism and comments on the earlier drafts of this thesis.

I am most grateful to Hewlett Packard Santa Clara Technology Center for giving me the opportunity to participate in the development of the HP1X multiplier and the MPC test chip, the use of their SPICE models in the research work and for their kind invitation to allow me to pursue my work in California. In particular, many thanks to Mr. Patrick Byrne for his advice and support during the work on the HP1X multiplier and MPC test chip, and his most helpful guidance during the initial stages of the research work. Also, my sincere gratitude to Mr. William Hillery for his criticism and continued interest in this work.

I am also greatly indebted to members of the IC Design Centre for their constant support, in particular to Mr. Brian Fantini for persevering with my computing demands.

Acknowledgements are due to the government of Malaysia for providing financial support without whom this work might not have been possible.

Last, but not least, I would like to thank my family who has encouraged me to do my best and provided comfort in times of difficulty.

#### **ABSTRACT**

With current trend towards single chip digital signal processors and the growing demand for more powerful and real time performance of such processors, further improvements in speed would need to be made on multipliers. iterative carry-save array (CSA) Considerable conventional speed of array multipliers can be achieved by adding increases in the more than one partial product bit at a time by employing higher order approach heavily depends on parallel (p,q) counters. This an efficient which ideally should have a delay and realisation of a counter, complexity comparable to that of a full-adder.

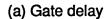

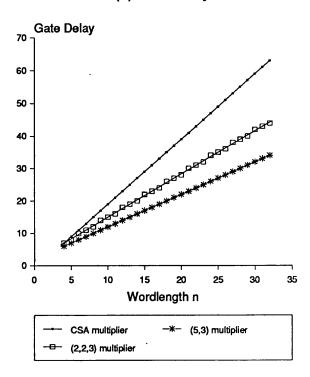

An iterative array multiplier which employs a (5,3) counter recently reported and based similar techniques, a novel on counter cells developed in this multiplier utilising (2,2,3)was project. (5,3)shows that both the counter and (2,2,3)counter study architectures are quite close to conventional array multipliers from VLSI implementation point of view. Assuming the counters operate at a comparable speed as a CSA full-adder, the (5,3) counter scheme is faster than conventional array multipliers by nearly a factor of two, while the technique offers significant improvements for (2,2,3)counter operand wordlength. In this work, the (5,3) counter and (2,2,3) counter were studied, principally on the efficiency of operation speed and viability of the array architectures in the fast bipolar ECL technology. For this purpose, a reconsideration of threshold logic, in view of better IC processes of today as well as the well-proven cascode ECL was investigated. A novel threshold circuit technique based on use of negative weighted inputs is proposed to overcome maximum fan-in weight limitation found in traditional threshold A method of mapping a logic function onto series gated ECL suitable for software implementation is presented. The work also includes the design of a 16 x 16-bit Booth-encoded multiplier and a test chip composed of ring oscillators, using state-of-the-art bipolar technology.

Simulation results show that the most efficient realisation cell implemented in series gated ECL using well-proven (2,2,3) counter gates. Circuit simulations indicate the (2,2,3) counter to be nearly as fast as a CSA full-adder. With such a realisation of the (2,2,3) counter improvements in the speed the (2,2,3)cell, significant of multiplier over that of conventional CSA multiplier can be expected, especially for large operand wordlengths.

## **CONTENTS**

|                                                                   | PAGE                        |

|-------------------------------------------------------------------|-----------------------------|

| Acknowledgements Abstract Contents List of Figures List of Tables | i<br>ii<br>iii<br>vii<br>xi |

| CHAPTER 1 INTRODUCTION                                            |                             |

| 1.1. Multipliers in digital signal processing                     | 1                           |

| 1.2. Silicon vs. GaAs                                             | 4                           |

| 1.3. Research objectives                                          | 7                           |

| 1.4. Outline of thesis                                            | 9                           |

| References                                                        | 11                          |

| CHAPTER 2 APPROACHES TO PARALLEL MULTIPLIER DESIGN                |                             |

| 2.1. Introduction                                                 | 16                          |

| 2.2. Traditional approaches to multiplier design                  | 17                          |

| 2.2.1. Parallel multiplication schemes                            | 18                          |

| 2.2.2. Fewer partial products                                     | 21                          |

| 2.2.3. Fast final adders                                          | 23                          |

| 2.2.4. Architectural comparisons                                  | 24                          |

| 2.3. Bounds on multiplication speed                               | 29                          |

| 2.4. Approaches to improve the speed                              | 31                          |

| 2.4.1. Parallel (p,q) counters                                    | 33                          |

| 2.4.2. Number of levels for reduction                             | 36                          |

| 2.4.3. Implementation and synthesis of parallel counters          | 38                          |

| 2.5. Further work needed                                          | 42                          |

| 2.6. Summary                                                      | 44                          |

| References                                                        | 45                          |

| CHAPTER 3 THE HP1X MULTIPLIER AND MPC TEST CHIP                                                                   |       |

|-------------------------------------------------------------------------------------------------------------------|-------|

| 3.1. Introduction                                                                                                 | 51    |

| 3.2. The HP1X's architecture                                                                                      | 51    |

| 3.3. The MPC test chip                                                                                            | 55    |

| 3.3.1. Results                                                                                                    | 59    |

| References                                                                                                        | 67    |

| Chapter 4 ARCHITECTURES FOR ITERATIVE ARRAY MULTIPLIC.                                                            | ATION |

| 4.1. Introduction                                                                                                 | 68    |

| 4.2. Extension of the CSA technique                                                                               | 70    |

| 4.2.1. (4,3) counter multiplier architectures                                                                     | 70    |

| 4.2.2. (5,3) counter multiplier architectures                                                                     | 73    |

| 4.3. An optimum (5,3) counter array multiplier                                                                    | 77    |

| 4.4. Novel iterative (2,2,3) counter multiplier architecture                                                      | 83    |

| 4.4.1. Architectural description of (2,2,3) counter multiplier                                                    | 86    |

| 4.4.2. Critical delay path                                                                                        | 94    |

| 4.4.2.1. Derivation of the weight of the critical intermediate product bit                                        | 96    |

| 4.4.2.2. A proof that the higher significant product bits have a delay not more than the delay of IP <sub>c</sub> | 98    |

| 4.5. Architectural comparisons of (5,3) and (2,2,3) counter multipliers                                           | 100   |

| 4.6. Summary                                                                                                      | 104   |

| References                                                                                                        | 105   |

| CHAPTER 5 REALISATION OF PARALLEL COUNTERS                                                                        |       |

| 5.1. Introduction                                                                                                 | 109   |

| 5.2. Design considerations of the (5,3) and (2,2,3) counters                                                      | 110   |

| 5.2.1. Emitter-coupled logic                                                                                      | 112   |

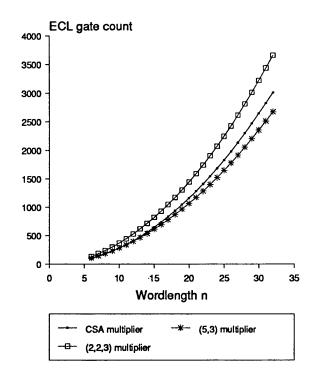

| 5.2.1.1. A technique for mapping a logic function onto cascode ECL                                                | 114   |

| 5.2.2. Threshold logic                                                    | 119 |

|---------------------------------------------------------------------------|-----|

| 5.3. (5,3) counter cell                                                   | 121 |

| 5.3.1. ECL implementation of a (5,3) counter                              | 121 |

| 5.3.2. Threshold logic implementation of a (5,3) counter                  | 129 |

| 5.4. (2,2,3) counter cell                                                 | 137 |

| 5.4.1. ECL implementation of a modified full-adder                        | 138 |

| 5.4.2. Threshold logic implementation of a modified full-adder            | 143 |

| 5.5. Summary                                                              | 144 |

| References                                                                | 145 |

| CHAPTER 6 SIMULATION RESULTS                                              |     |

| 6.1. Introduction                                                         | 149 |

| 6.2. (5,3) counter cell                                                   | 150 |

| 6.2.1. (5,3) counter realised in threshold logic                          | 150 |

| 6.2.1.1. Analysis of novel threshold circuit                              | 151 |

| 6.2.1.2. Estimation of unit weight voltage and maximum fan-in weight      | 153 |

| 6.2.1.3. SPICE results                                                    | 156 |

| 6.2.2. (5,3) counter implemented with ECL multiplexers                    | 161 |

| 6.3. (2,2,3) counter cell                                                 | 164 |

| 6.3.1. Modified full-adder implemented with 4-level ECL gates             | 165 |

| 6.3.2. Modified full-adder implemented with AND gate-normal full-adder    | 168 |

| 6.3.3. Comparisons of the two implementations of a modified full-adder    | 172 |

| 6.4. Speed comparisons of (2,2,3) counter and conventional CSA multiplier | 175 |

| 6.4.1. Delay characteristics of ECL gates                                 | 175 |

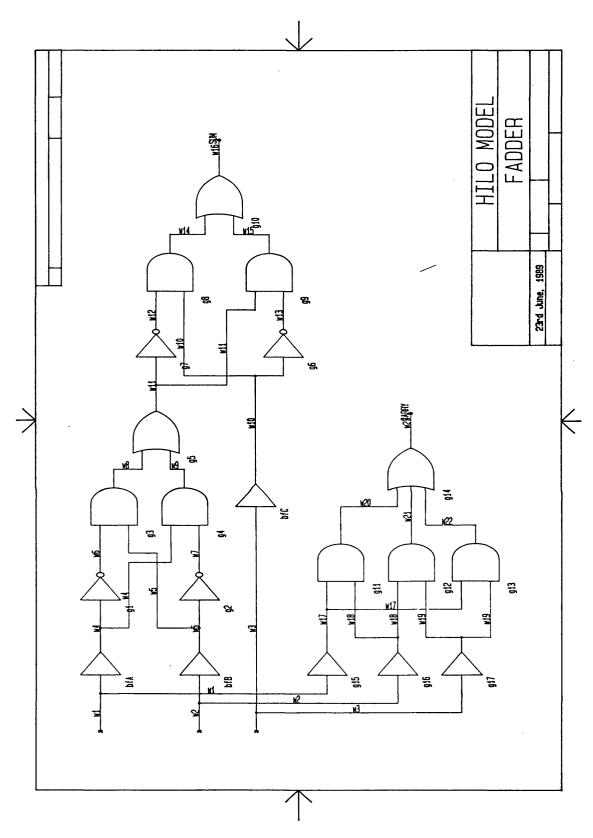

| 6.4.2. Modelling the delay behaviour of ECL gates in HILO                 | 178 |

| 6.4.3. HILO simulation results                                            | 179 |

| 6.5. Summary                                                              | 189 |

| References                                                                | 190 |

# CHAPTER 7 CONCLUSIONS AND RECOMMENDATIONS FOR FUTURE WORK

| 7.1. Background                                            | 191 |

|------------------------------------------------------------|-----|

| 7.2. Research summary                                      | 193 |

| 7.3. Conclusions and discussions                           | 195 |

| 7.4. Recommendations for future work                       | 198 |

| References                                                 | 201 |

| APPENDIX A HP1X SPICE models                               | 204 |

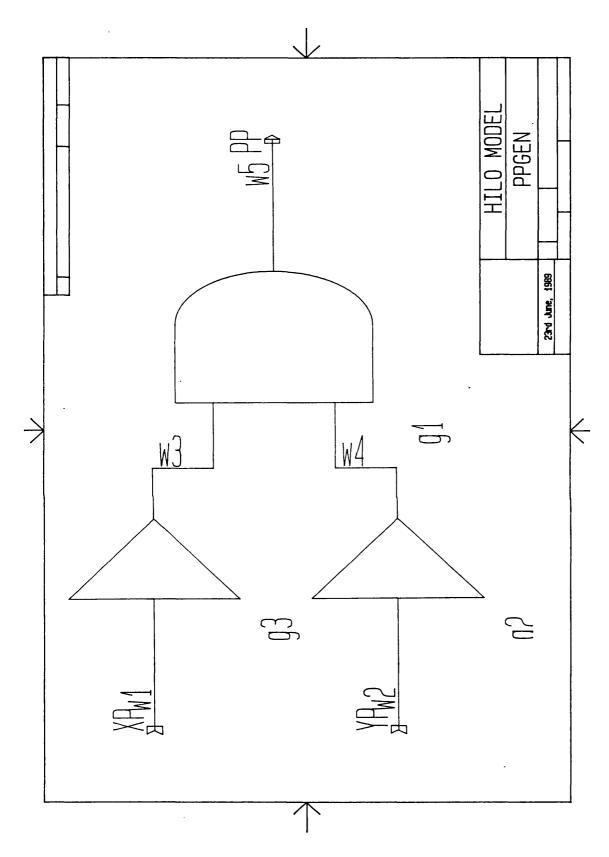

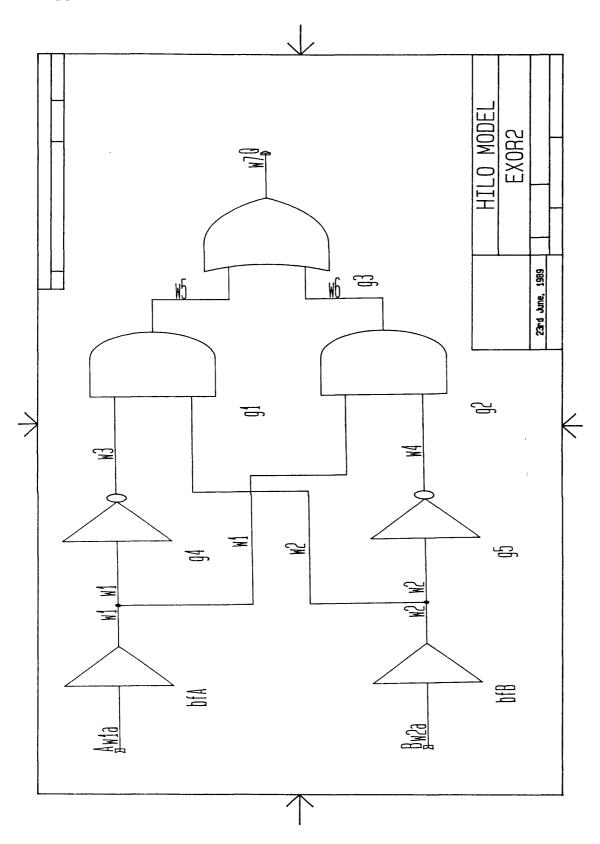

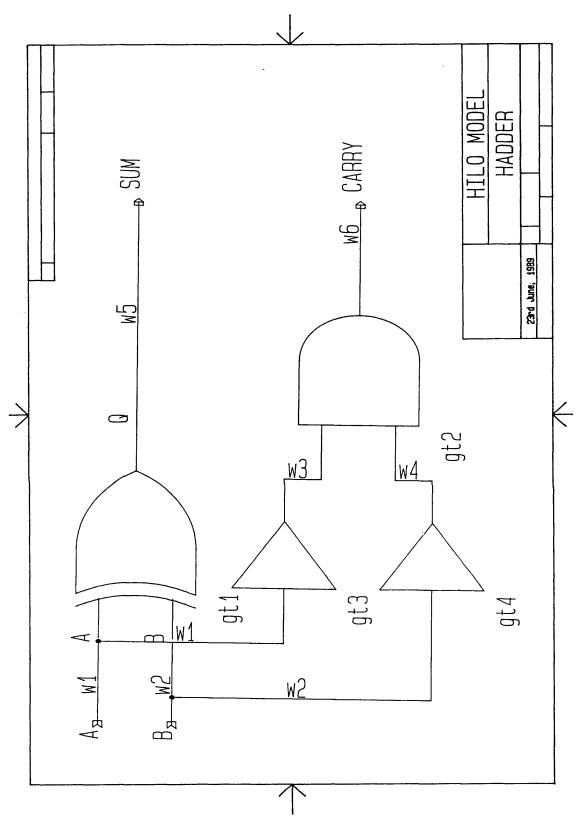

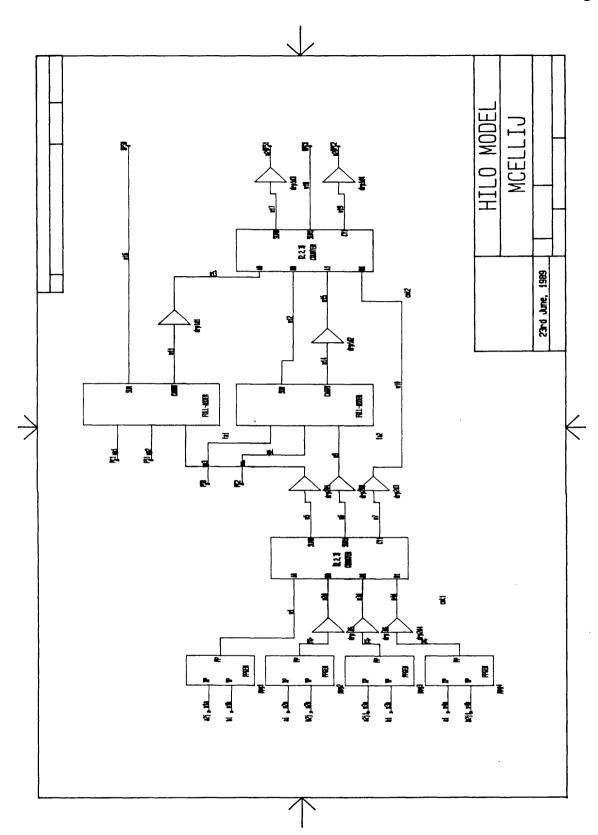

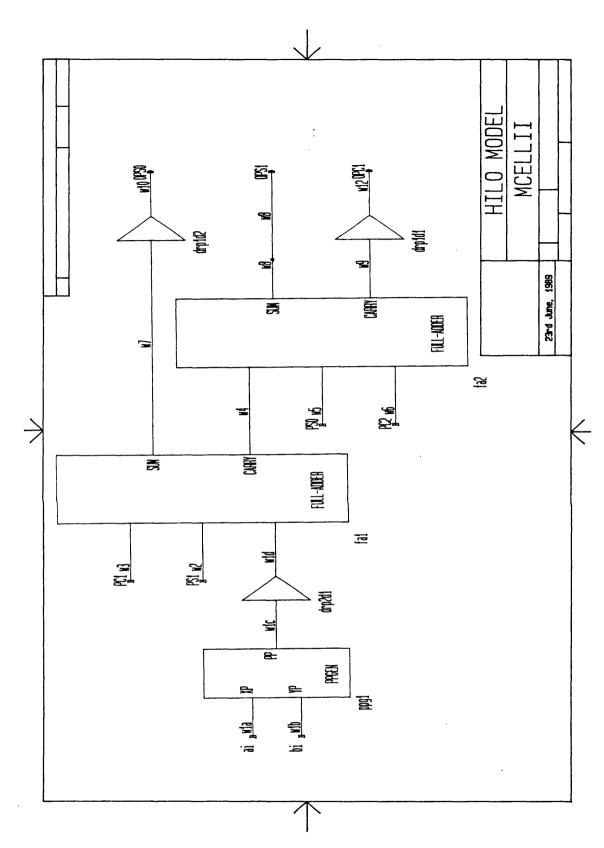

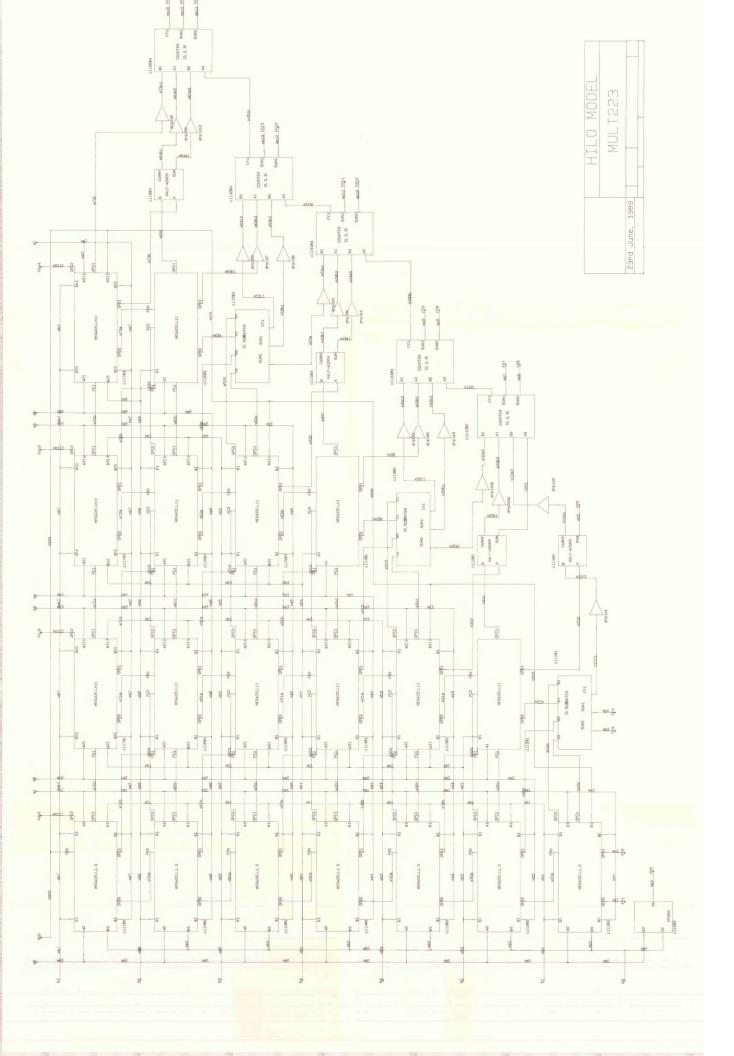

| APPENDIX B-1 HILO subfiles of CSA multiplier               | 206 |

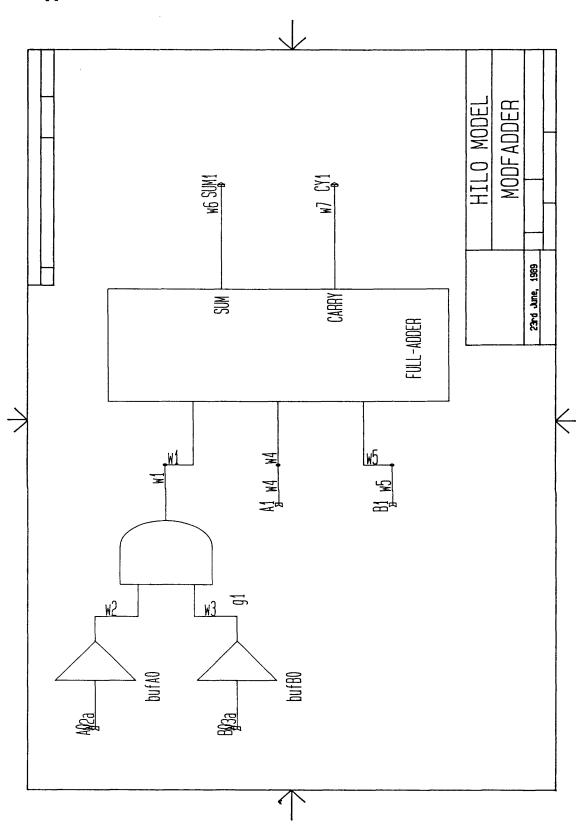

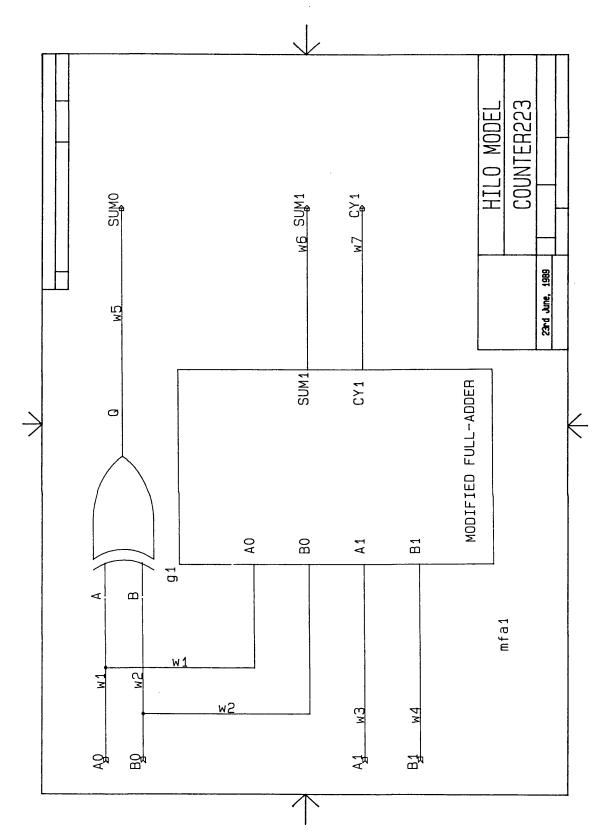

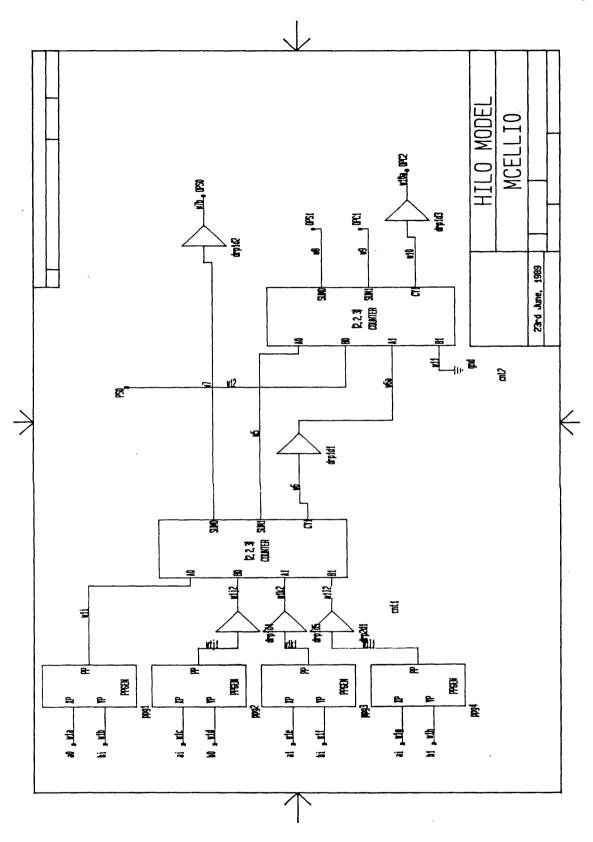

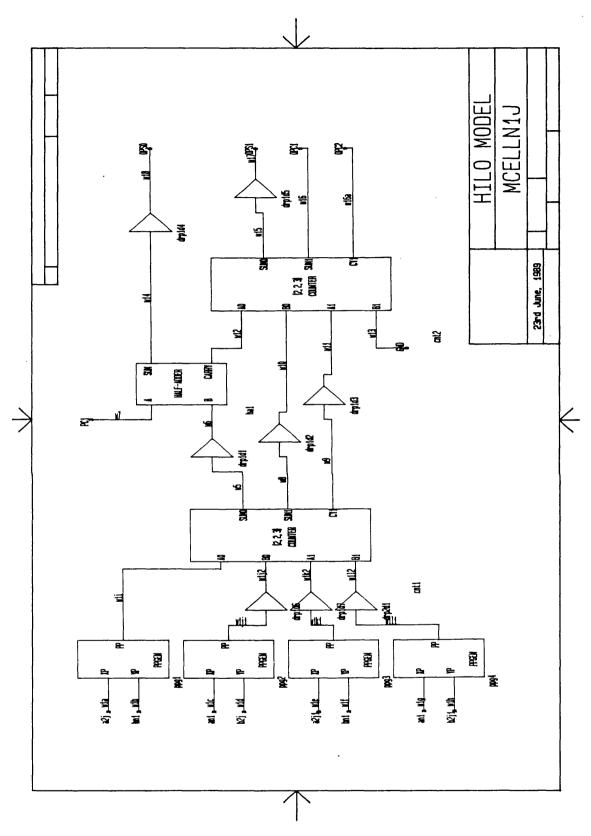

| APPENDIX B-2 HILO subfiles of (2,2,3) counter multiplier   | 211 |

| APPENDIX B-3 HILO schematics of (2,2,3) counter multiplier | 221 |

## LIST OF FIGURES

| Figure                                                                                                                                              | Page     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------|

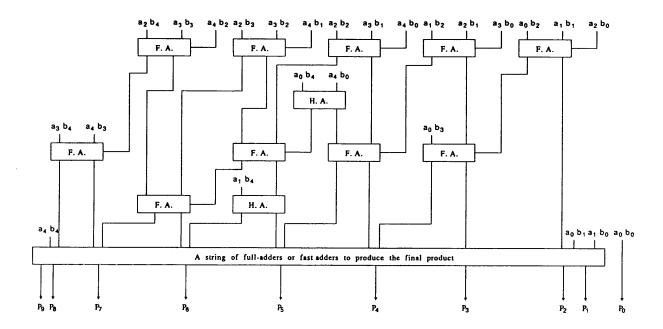

| 2.1. Block diagram of a 5 x 5-bit multiplier using CSA technique [2.15].                                                                            | 19       |

| 2.2. Block diagram of a 5 x 5-bit multiplier using Wallace's scheme [2.15].                                                                         | 21       |

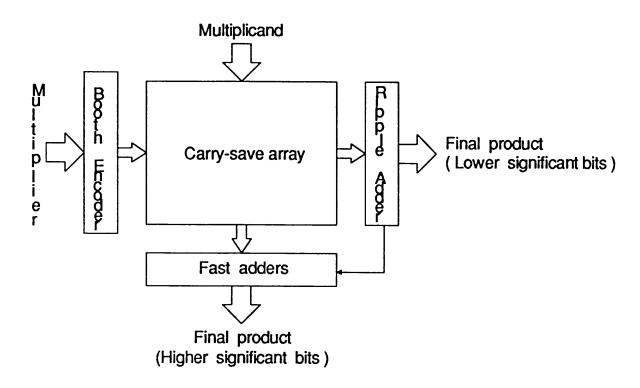

| 2.3. Block diagram of a typical high-speed multiplier.                                                                                              | 26       |

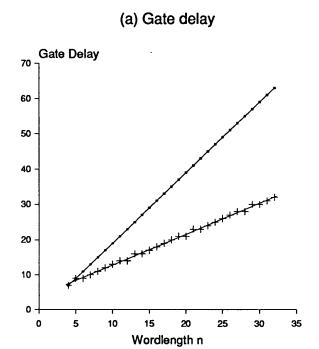

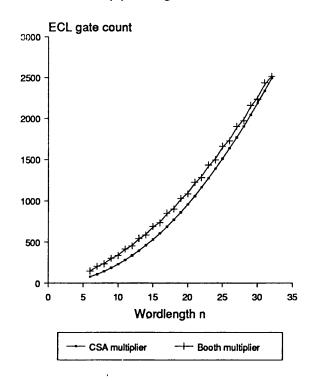

| 2.4. (a) Relative gate delay and (b) ECL gate count of a straight CSA multiplier and Booth-encoded CSA multiplier with fast final adders.           | 28       |

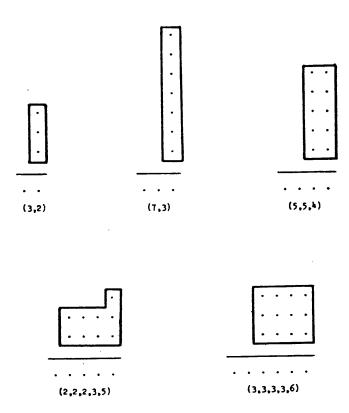

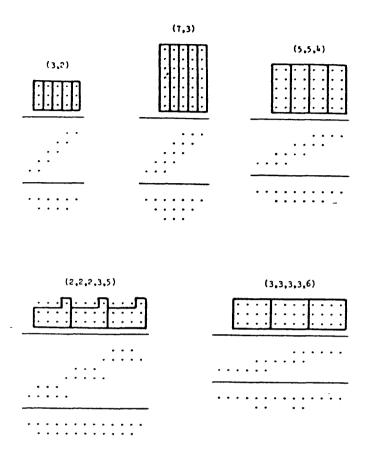

| 2.5. Some generalized counters [2.17].                                                                                                              | 34       |

| 2.6. Effect of a series of adjacent counters [2.17].                                                                                                | 35       |

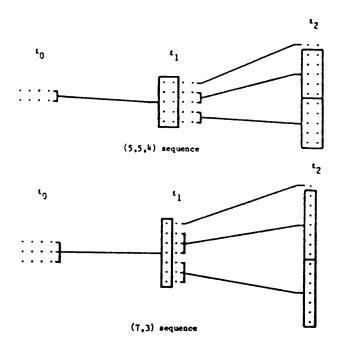

| 2.7. Examples of multi-level reduction [2.17].                                                                                                      | 37       |

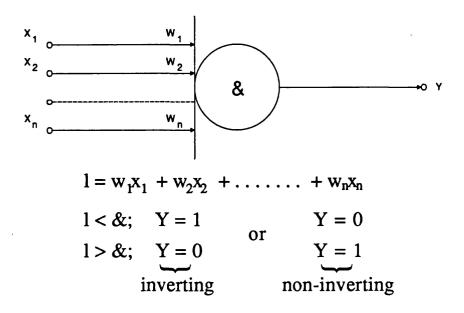

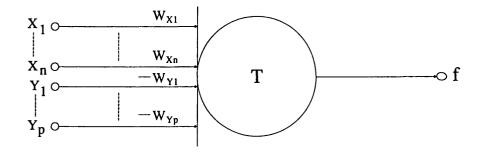

| 2.8. The logical definition of threshold gates [2.69].                                                                                              | 41       |

| <b>2.9.</b> A (n,3) counter using inverting threshold logic [2.25]. (where $4 \le n \le 7$ )                                                        | 41       |

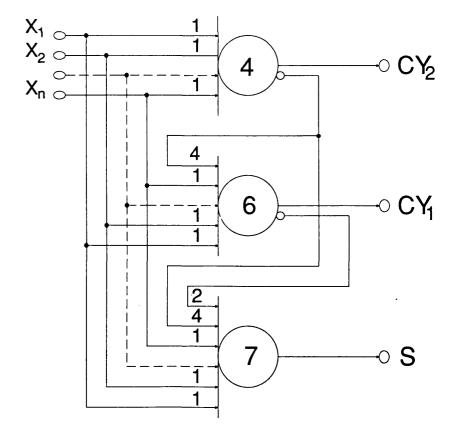

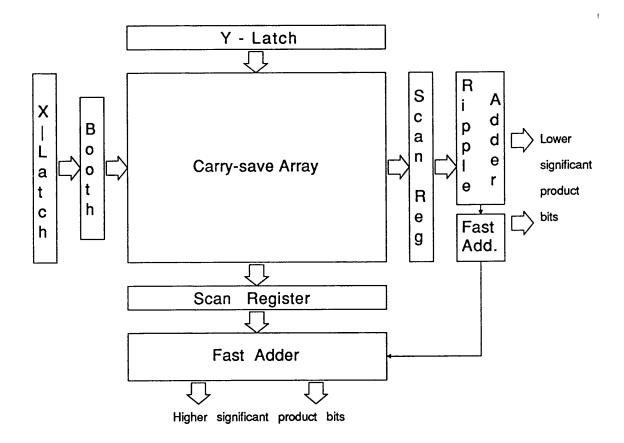

| 3.1. Block diagram of the HP1X multiplier.                                                                                                          | 52       |

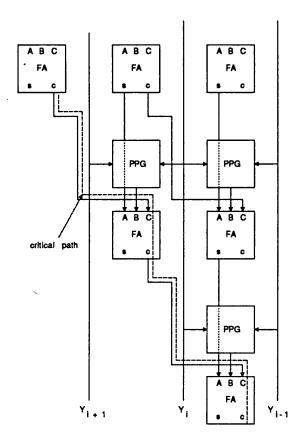

| 3.2. Part of the carry-save array.                                                                                                                  | 53       |

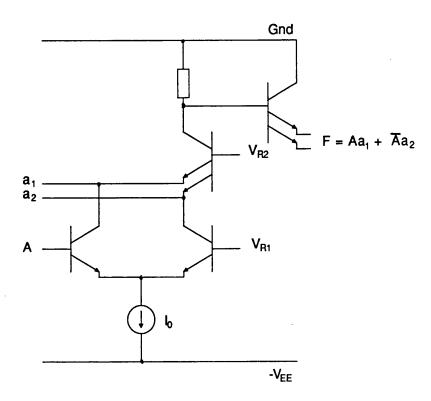

| 3.3. A simple EFL structure [3.3].                                                                                                                  | 54       |

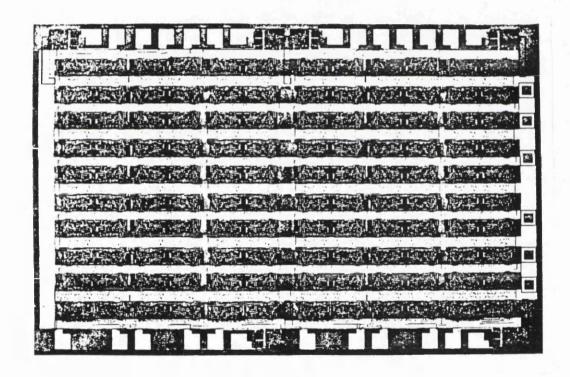

| 3.4. Microphotograph of MPC test chip.                                                                                                              | 55       |

| 3.5. A 20-stage ring oscillator.                                                                                                                    | 56       |

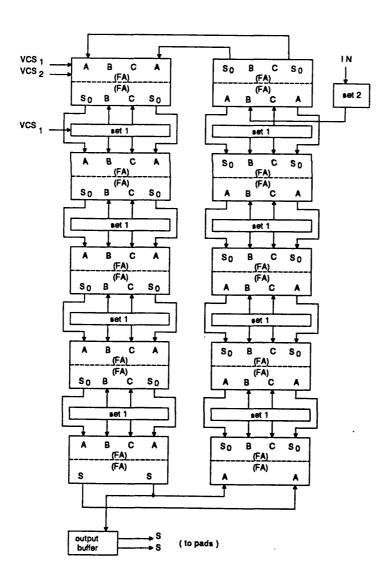

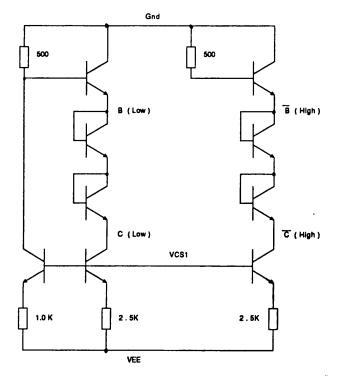

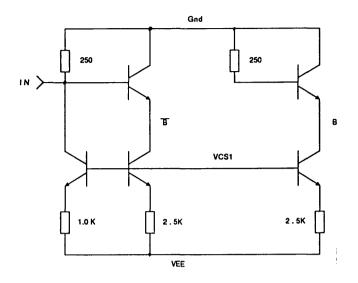

| 3.6. (a) Full-adder schematic (b) SET1 schematic (c) SET2 schematic (d) Output buffer schematic.                                                    | 57<br>58 |

| 3.7. Propagation delay of ring oscillator 1; Load resistance=500Ω; Transistor emitter size=1x10μm. (a) Measured, and (b) Simulated.                 | 61       |

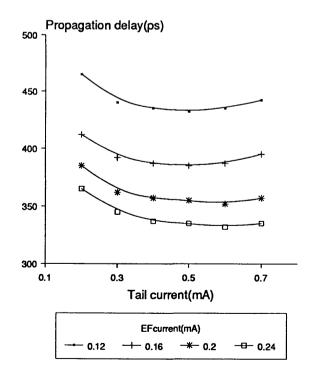

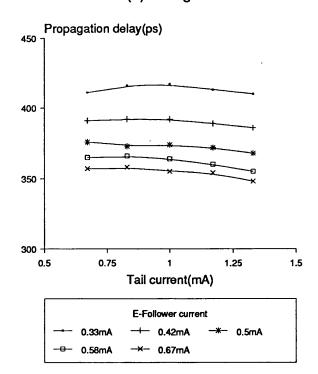

| 3.8. Propagation delay of ring oscillator 2; Load resistance=500Ω; Transistor emitter size=1x5μm. (a) Measured, and (b) Simulated.                  | 62       |

| 3.9. Propagation delay of ring oscillator 3; Load resistance=250Ω; Transistor emitter size=1x10μm. (a) Measured, and (b) Simulated.                 | 63       |

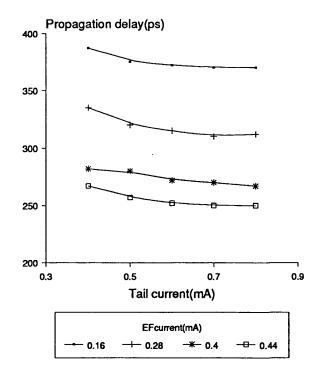

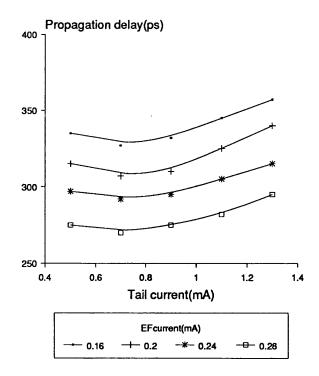

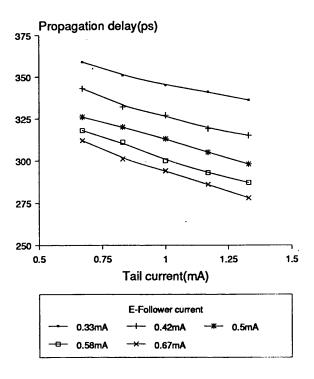

| 3.10. Propagation delay of ring oscillator 4; Load resistance= $250\Omega$ ; Transistor emitter size= $1x5\mu m$ . (a) Measured, and (b) Simulated. | 64       |

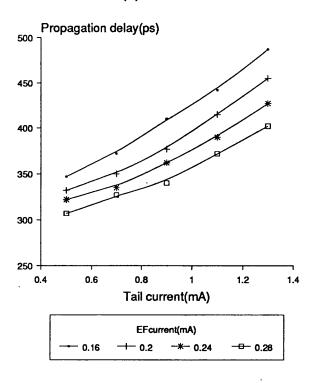

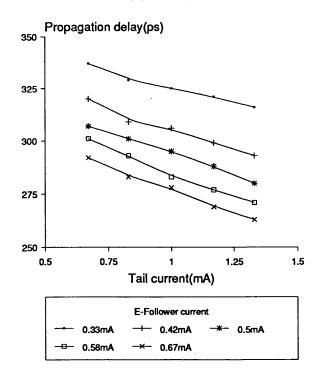

| 3.11. Propagation delay of ring oscillator 5; Load resistance=750Ω; Transistor emitter size=1x10um. (a) Measured, and (b) Simulated.                | 65       |

| Figure                                                                                                                                                                                                               | Page      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

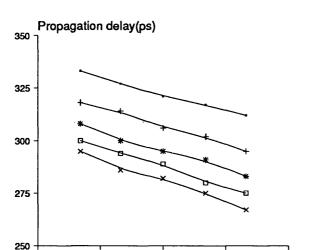

| 3.12. Propagation delay of ring oscillator 6; Load resistance=750Ω; Transistor emitter size=1x5μm. (a) Measured, and (b) Simulated.                                                                                  | 66        |

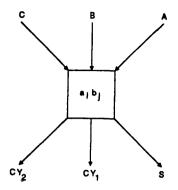

| 4.1. (a) A (4,3) counter cell (b) A 8 x 8-bit (4,3) counter CSA multiplier.                                                                                                                                          | 71        |

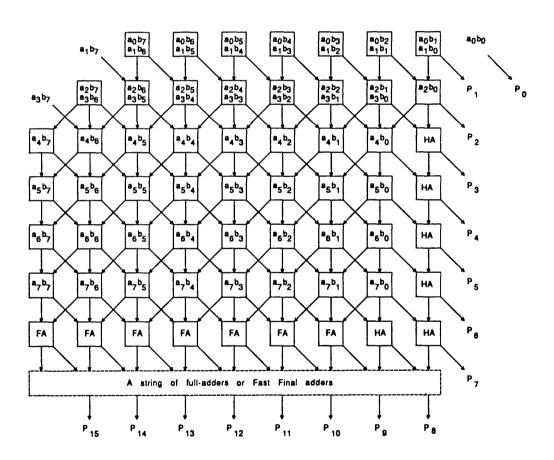

| 4.2. (a) A (5,3) counter cell (b) A 8 x 8-bit (5,3) counter CSA multiplier.                                                                                                                                          | 74        |

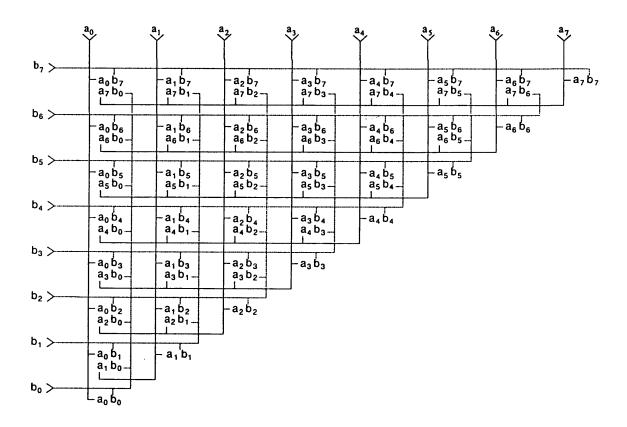

| 4.3. A 8 x 8-bit collated square array of partial product bits [4.27].                                                                                                                                               | 78        |

| 4.4. A 8 x 8-bit folded triangle array of partial product bits [4.27].                                                                                                                                               | 78        |

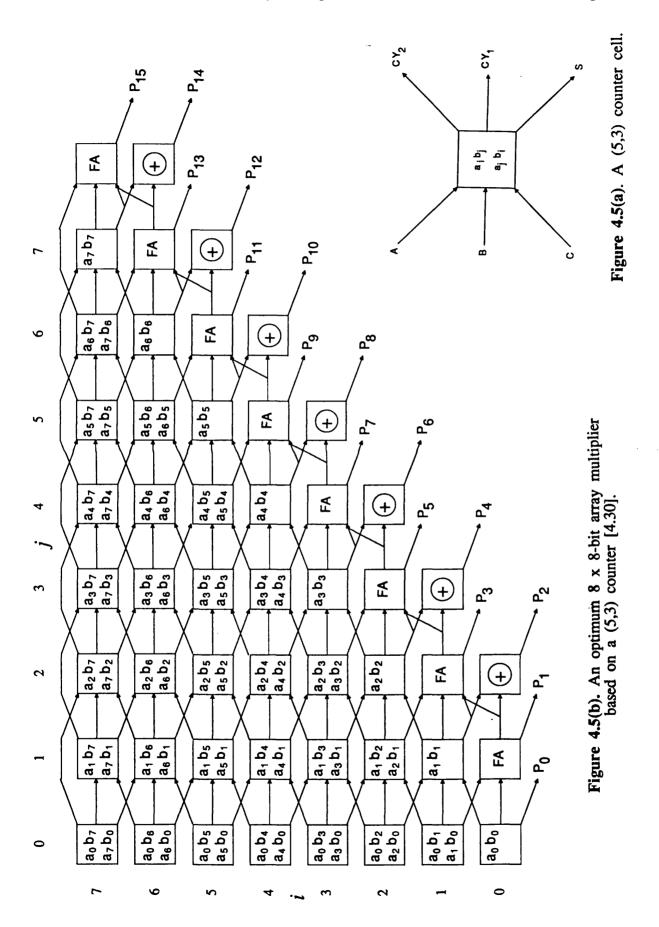

| 4.5. (a) A (5,3) counter cell (b) An optimum 8 x 8-bit array multiplier based on a (5,3) counter [4.30].                                                                                                             | <b>79</b> |

| 4.6. Distribution and wiring of partial product terms.                                                                                                                                                               | 82        |

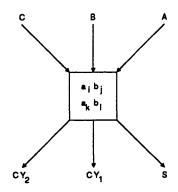

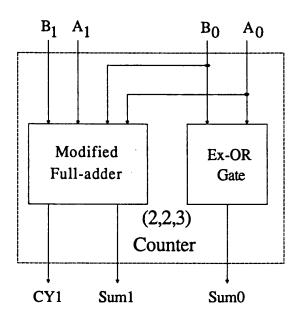

| 4.7. A (2,2,3) counter cell.                                                                                                                                                                                         | 85        |

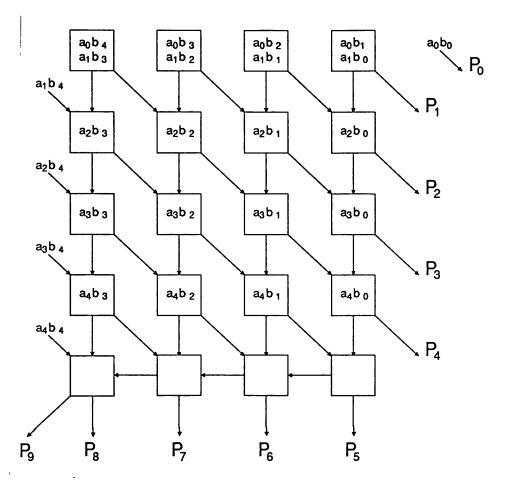

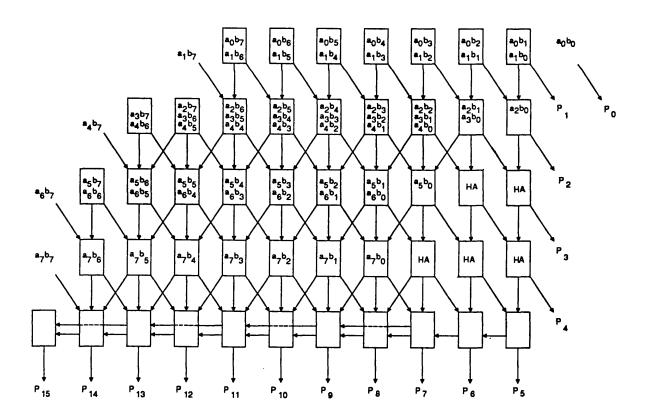

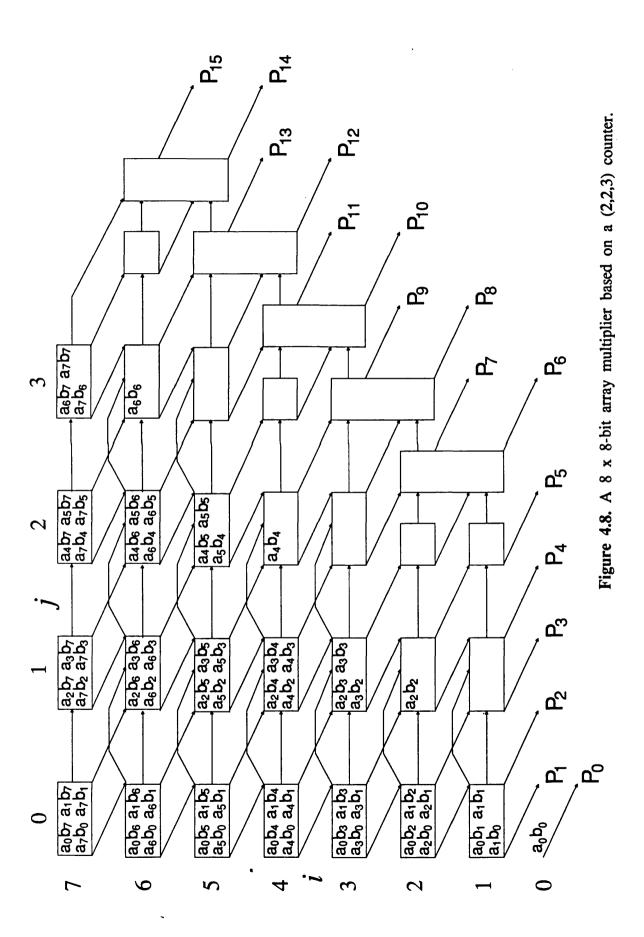

| 4.8. A 8 x 8-bit array multiplier based on a (2,2,3) counter.                                                                                                                                                        | 87        |

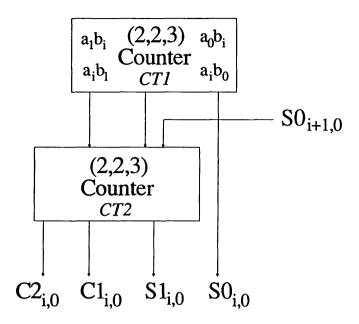

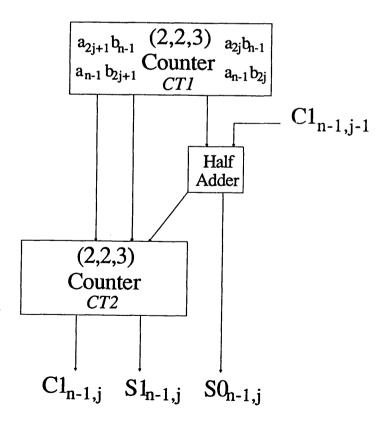

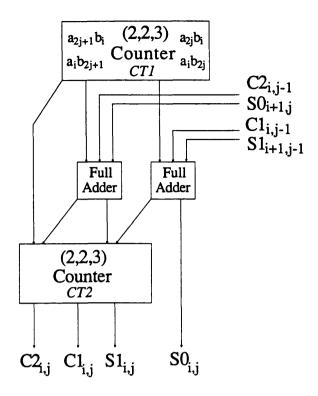

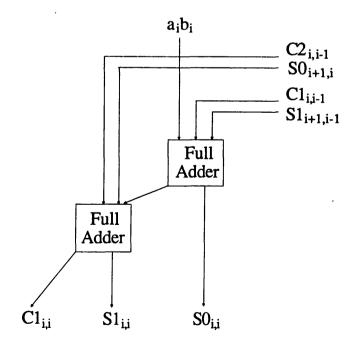

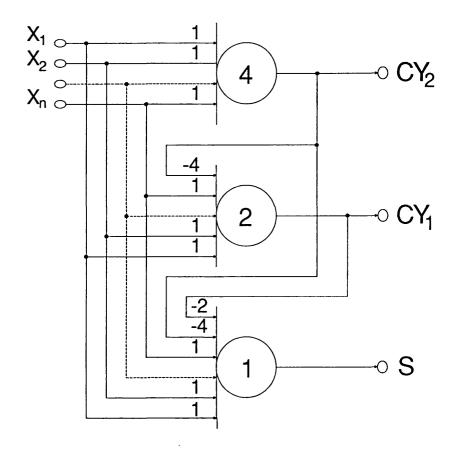

| <ul> <li>4.9. (a) Composition of megacell C<sub>i,0</sub> (b) Composition of megacell C<sub>n-1,j</sub></li> <li>(c) Composition of megacell C<sub>i,j</sub> (d) Composition of megacell C<sub>i,i</sub>.</li> </ul> | 88<br>89  |

| 4.10. A network of half-adders and (2,2,3) counters for the diagonal cells.                                                                                                                                          | 92        |

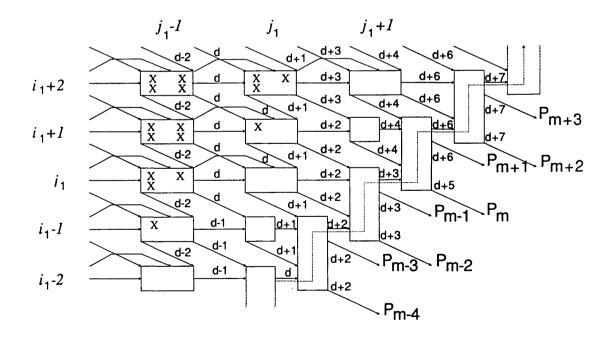

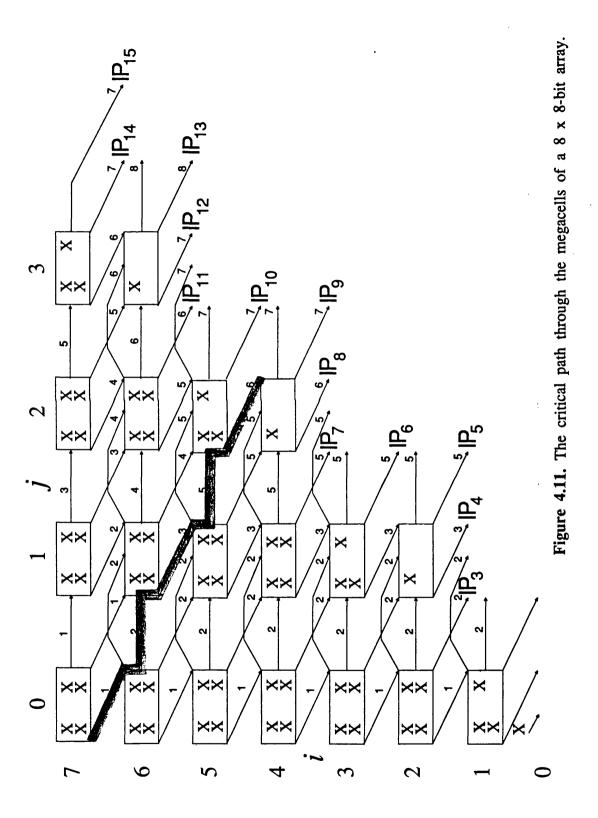

| 4.11. The critical path through the megacells of a 8 x 8-bit array.                                                                                                                                                  | 95        |

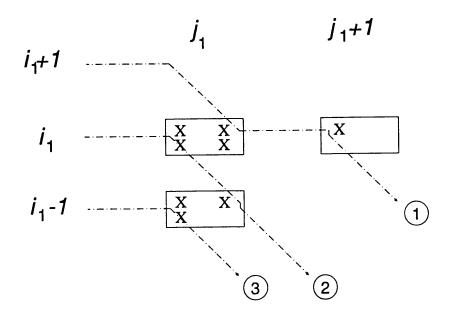

| <b>4.12.</b> Diagram demonstrating possible paths where $IP_c$ ends.                                                                                                                                                 | 96        |

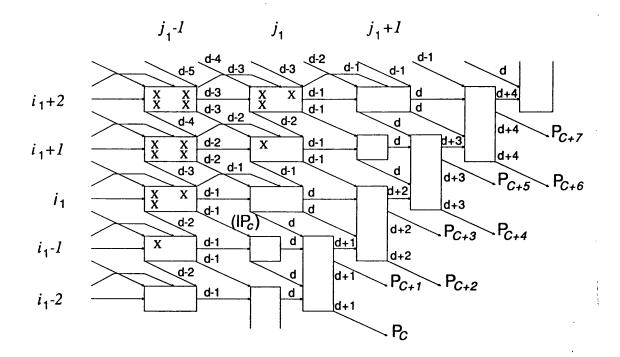

| <b>4.13.</b> Part of an array above the critical delay path $IP_c$ .                                                                                                                                                 | 98        |

| 4.14. A comparison of different array multiplier schemes. (a) Relative gate delay, and (b) ECL gate count.                                                                                                           | 102       |

| 5.1. A differential switch equivalent symbol.                                                                                                                                                                        | 114       |

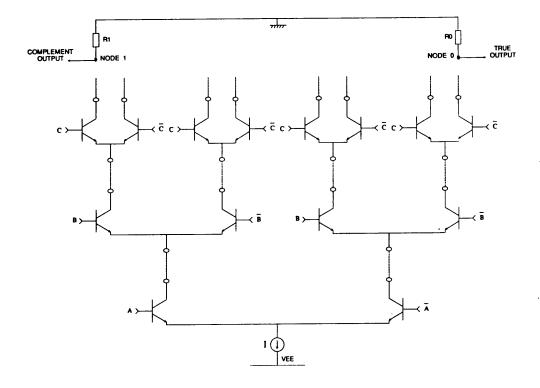

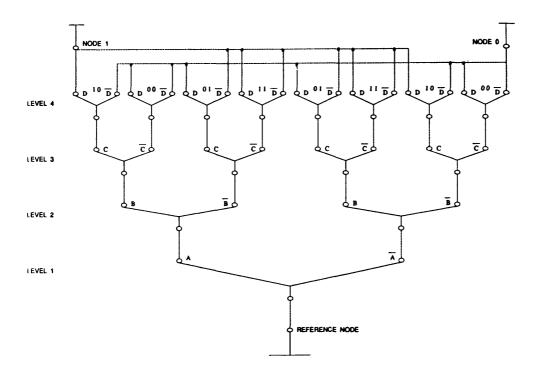

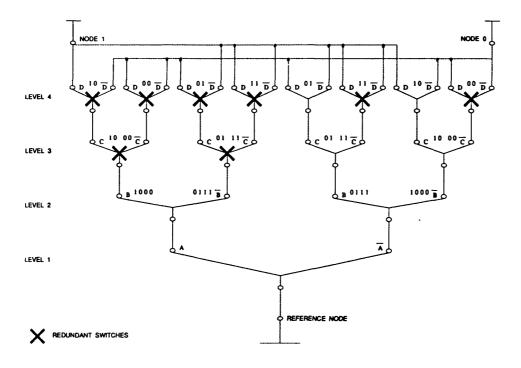

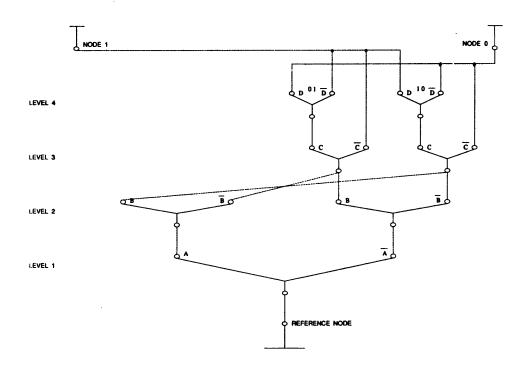

| <ul><li>5.2. (a) The possible current paths for a 3-variable function.</li><li>(b) Equivalent electrical schematic.</li></ul>                                                                                        | 115       |

| 5.3. (a) A full-blown tree of the CY1 function of a (2,2,3) counter (b) Identification and elimination of redundant switches.                                                                                        | 117       |

| (c) A minimized tree of the same function.                                                                                                                                                                           | 118       |

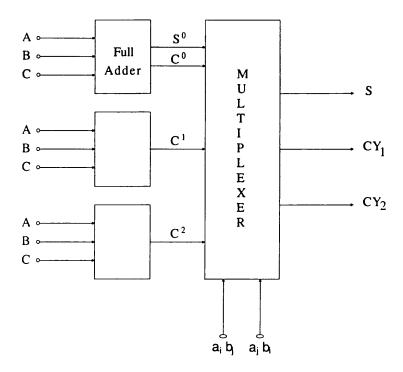

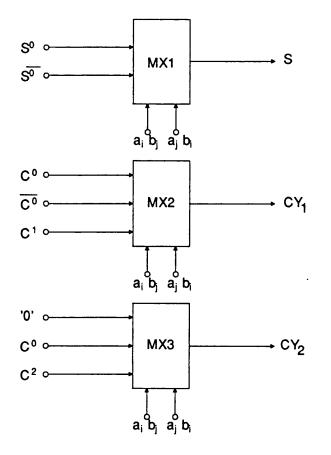

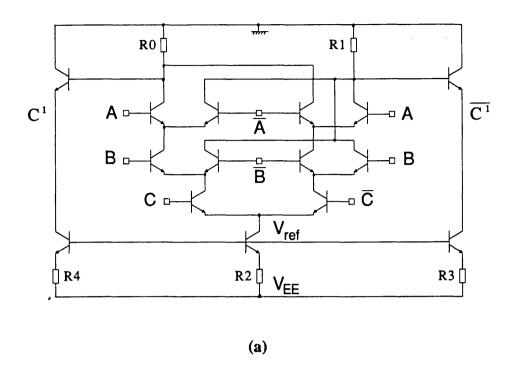

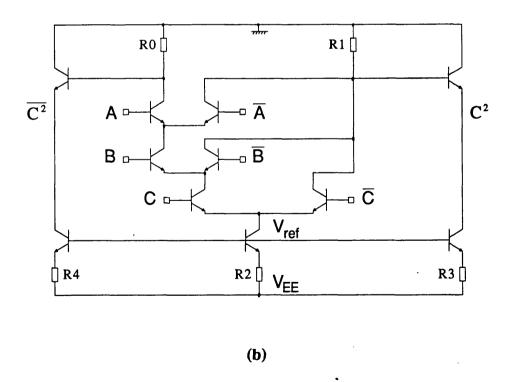

| 5.4. (a) An optimized logic design of a (5,3) counter (b) Multiplexers for the (5,3) counter.                                                                                                                        | 123       |

| Figure                                                                                                                                                                                                               | Page              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

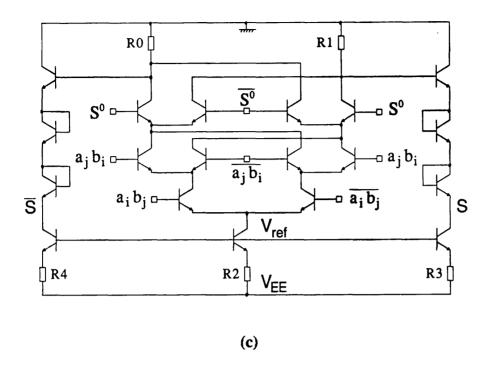

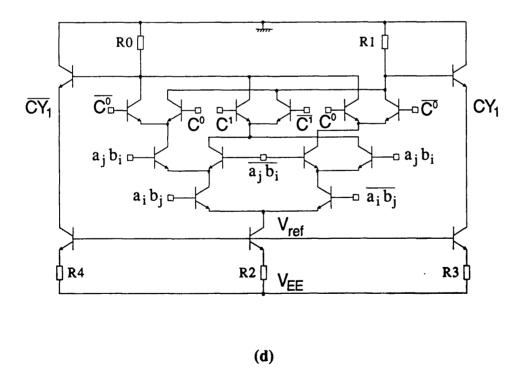

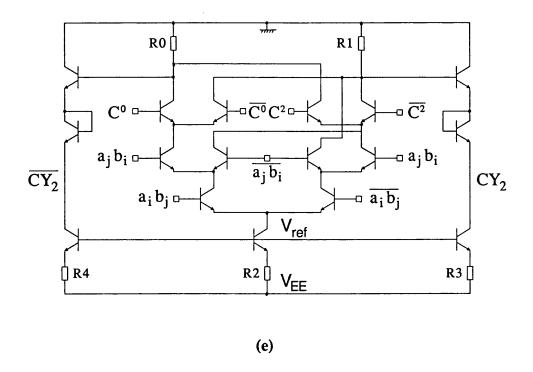

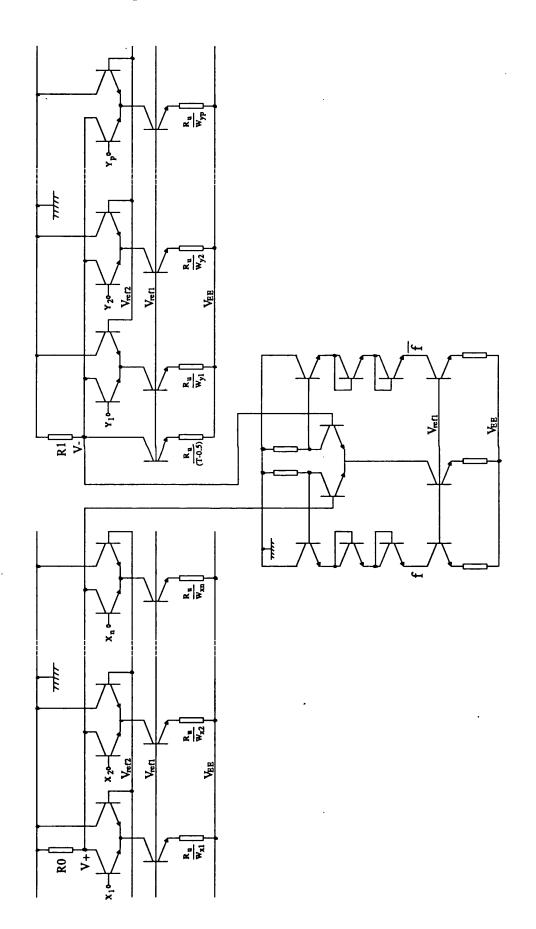

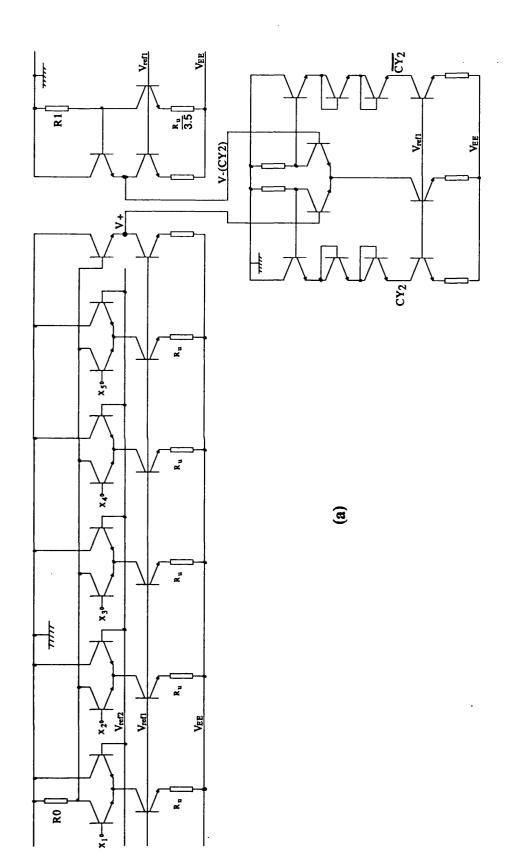

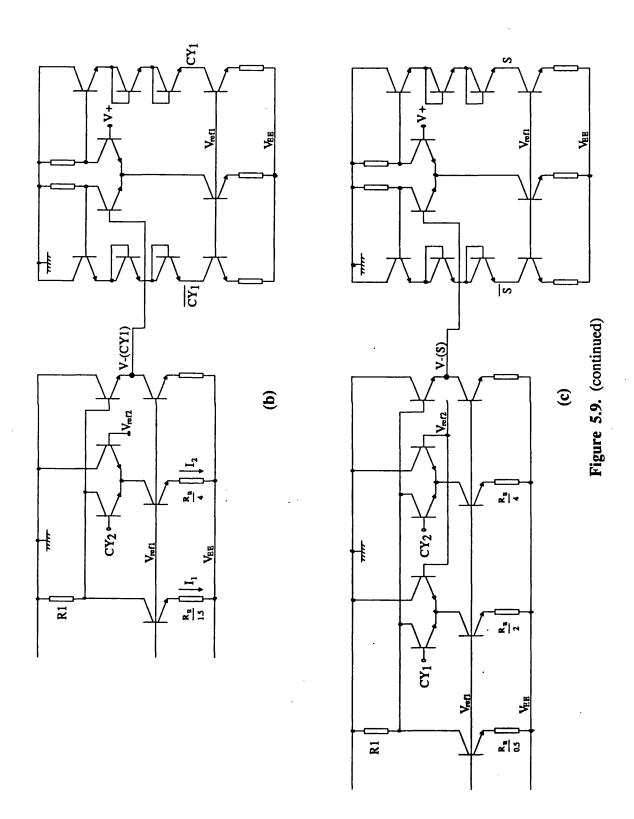

| <ul> <li>5.5. ECL implementation of the various logic blocks of a (5,3) counter.</li> <li>(a) C<sup>1</sup> gate, (b) C<sup>2</sup> gate,</li> <li>(c) MX1 gate, (d) MX2 gate,</li> <li>and (e) MX3 gate.</li> </ul> | 125<br>126<br>127 |

| 5.6. Alternative threshold logic realization of a $(n,3)$ counter (where $4 \le n \le 7$ )                                                                                                                           | 130               |

| 5.7. Threshold gate symbol with positive and negative weighted inputs.                                                                                                                                               | 130               |

| 5.8. A novel threshold logic circuit technique to realise positive and negative weighted inputs.                                                                                                                     | 131               |

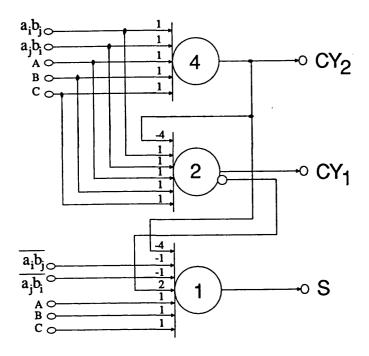

| 5.9. Implementation of a (5,3) counter using the new threshold circuit.  (a) CY <sub>2</sub> function                                                                                                                | 134               |

| (b) CY <sub>1</sub> function, and (c) S function.                                                                                                                                                                    | 135               |

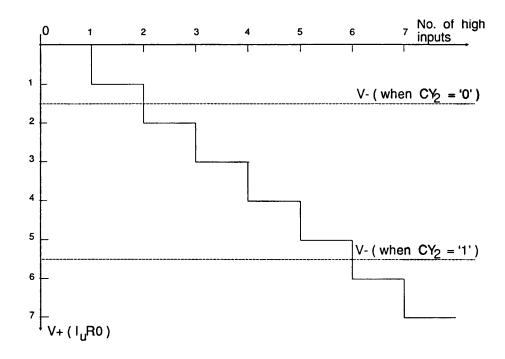

| 5.10. Graph showing the ideal characteristics of V+ and V- vs. no. of high inputs, of the CY <sub>1</sub> gate.                                                                                                      | 136               |

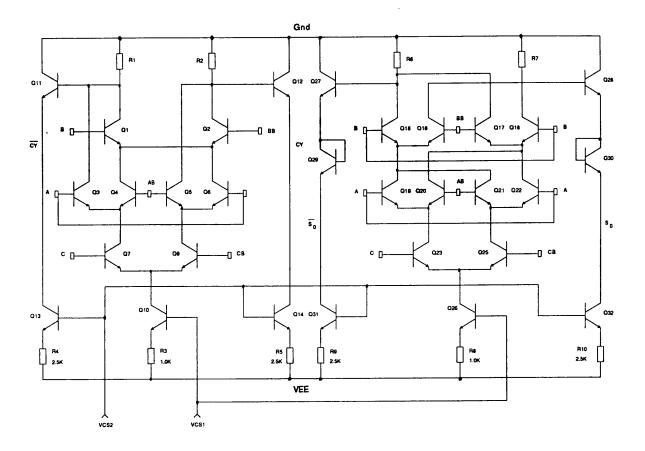

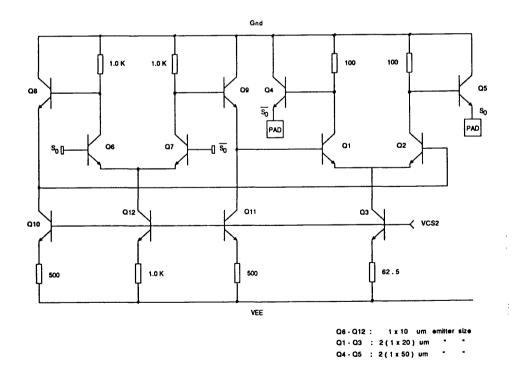

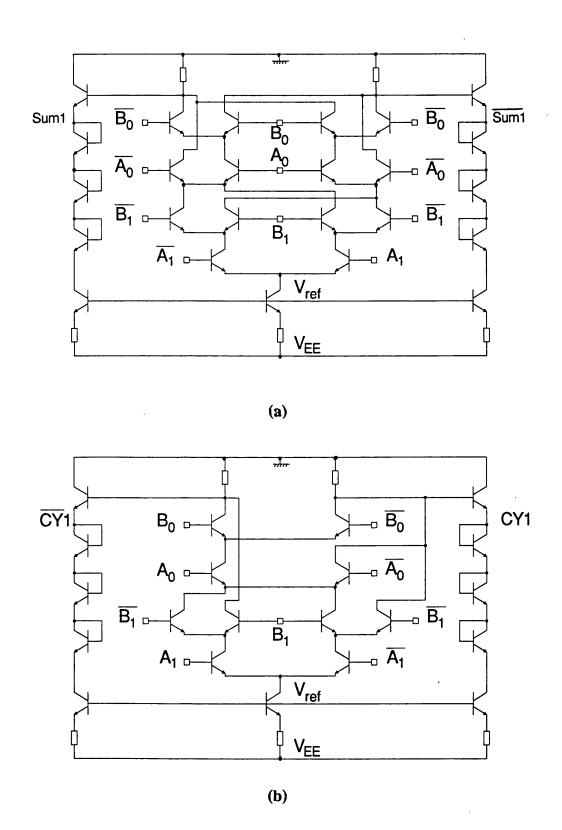

| 5.11. Implementation of the modified full-adder of a (2,2,3) counter by 4-level series gated ECL. (a) Sum1 gate, and (b) CY1 gate.                                                                                   | 139               |

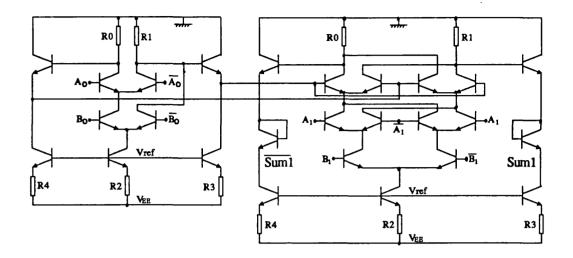

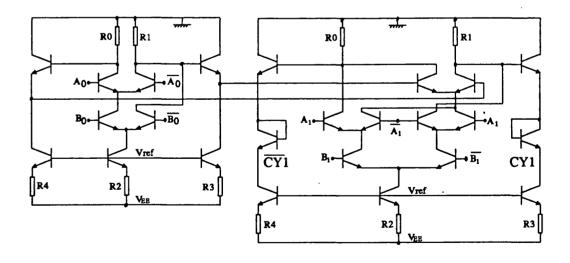

| <ul><li>5.12. Implementation of the modified full-adder of a (2,2,3) counter by using AND gate and normal full-adder. (a) Sum1 function, and (b) CY1 function.</li></ul>                                             | 140               |

| 5.13. A 4-level transistor tree showing node voltages.                                                                                                                                                               | 141               |

| 5.14. Threshold logic realization of a modified full-adder.                                                                                                                                                          | 144               |

| 6.1. Differential output as a function of differential input driving the comparators switch.                                                                                                                         | 155               |

| 6.2. Worst-case delay characteristics of threshold logic (5,3) counter.                                                                                                                                              | 158               |

| 6.3. Alternative threshold logic configuration of a (5,3) counter to improve propagation delay.                                                                                                                      | 160               |

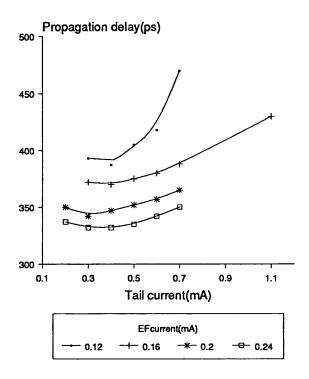

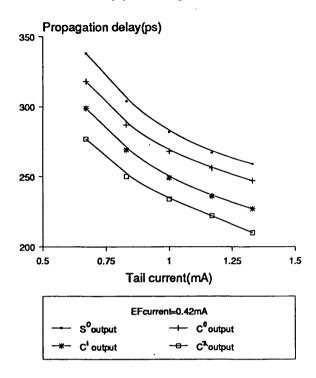

| <ul><li>6.4. Critical delay of various gates of a ECL (5,3) counter.</li><li>(a) 1st stage cells, and (b) Multiplexers MX1, MX2 and MX3.</li></ul>                                                                   | 162               |

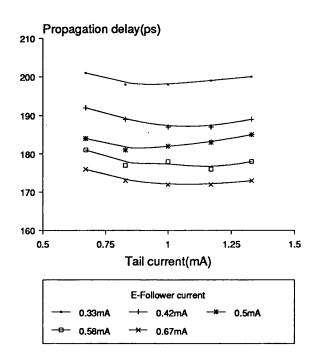

| 6.5. Critical delay of a 2-input EXOR series-gated ECL gate (Fanout=1).                                                                                                                                              | 165               |

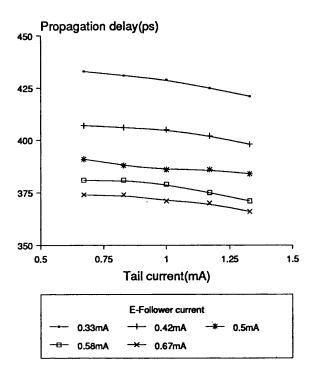

| 6.6. Worst-delay of a modified full-adder implemented with 4-level series gated ECL gate when all four differential levels switch (Fanout=1). (a) Sum1 gate, and (b) CY1 gate.                                       | 166               |

| Figure                                                                                                                                                                                                | Page |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| <ul><li>6.7. Worst-case delay of a modified full-adder implemented with 4-level series gated ECL when three differential levels switch (Fanout=1).</li><li>(a) Sum1 gate, and (b) CY1 gate.</li></ul> | 167  |

| 6.8. Worst-case delay of a modified full-adder implemented with AND gate -normal full-adder when input B <sub>1</sub> to full-adder changes (Fanout=1).                                               |      |

| (a) Sum1 gate, and (b) CY1 gate.                                                                                                                                                                      | 169  |

| 6.9. Worst-case delay of a modified full-adder implemented with AND gate -normal full-adder when input B <sub>0</sub> to AND gate changes (Fanout=1).                                                 |      |

| (a) Sum1 gate, and (b) CY1 gate.                                                                                                                                                                      | 170  |

| 6.10. Worst-case delay of a 2-input AND series gated ECL gate (Fanout=1).                                                                                                                             | 171  |

``

# LIST OF TABLES

| Table                                                                                                                                                           | Page |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1. Speed-power of Si bipolar and GaAs ring oscillators.                                                                                                       | 6    |

| 1.2. Speed-power of Si bipolar and GaAs 1K RAM.                                                                                                                 | 6    |

| 1.3. Speed-power of Si bipolar and GaAs 8 x 8-bit array multipliers.                                                                                            | 6    |

| 2.1. A modified Booth algorithm.                                                                                                                                | 22   |

| 2.2. Relative speeds of fast adder architectures.                                                                                                               | 24   |

| 2.3. Speed and ECL gate count of straight CSA multiplier and Booth-encoded CSA multiplier with fast final adders.                                               | 27   |

| 3.1. Truth-table of the sum function of a full-adder.                                                                                                           | 59   |

| 4.1. Truth-table of a (4,3) counter.                                                                                                                            | 72   |

| 4.2. Truth-table of a (5,3) counter.                                                                                                                            | 75   |

| 4.3. No. of counters for a n x n-bit (5,3) counter multiplier.                                                                                                  | 81   |

| 4.4. Truth-table of a (2,2,3) counter.                                                                                                                          | 85   |

| 4.5. Propagation delay of megacells.                                                                                                                            | 92   |

| <ul><li>4.6. (a) No. of megacells/counters of (2,2,3) counter multiplier.</li><li>(b) Total no. of parallel counters of a (2,2,3) counter multiplier.</li></ul> | 93   |

| 4.7. The weight and delay of the critical intermediate product bit over a range of wordlength.                                                                  | 97   |

| 4.8. ECL gate count estimate of (2,2,3) counter multiplier and (5,3) counter multiplier.                                                                        | 101  |

| 5.1. Minimized logic function of a (5,3) counter.                                                                                                               | 122  |

| 5.2. Logic table of a (6,3) counter.                                                                                                                            | 128  |

| 5.3. Logic table of a (7,3) counter.                                                                                                                            | 128  |

| 6.1. Truth-table of a (5,3) counter in terms of no. of high inputs.                                                                                             | 157  |

| 6.2. Worst-case delays of a threshold (5,3) counter.                                                                                                            | 159  |

| 6.3. Delays of a 2-input AND and 2-input EXOR gate for fanout=2 (Tail current=1mA; Emitter follower current=0.5mA)                                              | 177  |

| 6.4. Delays of sum and carry gate of a full-adder for fanout=2 (Tail current=1mA; Emitter follower current=0.5mA).                                              | 177  |

| Table                                                                                                                                                               | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 6.5. HILO simulation results of a 8 x 8-bit CSA multiplier.                                                                                                         | 180  |

| 6.6. HILO simulation results of a 8 x 8-bit (2,2,3) counter multiplier.                                                                                             | 183  |

| 6.7. Total ECL gate count of (2,2,3) counter multiplier (where modified full-adder is implemented with AND gate-normal full-adder) and conventional CSA multiplier. | 188  |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1. Multipliers in digital signal processing

processing required In the past, most digital signal has that recorded and processed off-line digitized signals be then on general-purpose computers. In many cases, however, on-line, real-time and therefore very fast processing is required if digital techniques are successfully replace analog techniques. digital signal processing. In a sampled point of the analyzed waveform may require one addition and one multiplication. For example, if the analog signal is quantized into eight bits, the required computation is made up of nine additions - one for the real addition and eight simulating a multiplication. It is evident if the multiplication speed were to match the addition speed. bandwidth of the signal processor would increase significantly allowing more complex functions to be computed in real-time, and thus the ultimate limitation on performance of digital signal processors (DSP) is multiplication.

Over the years many multiplication algorithms have been proposed and practically used. Major advances in the realizations of multipliers monolithic integrated circuits over the past 10 years have done much to reduce multiplier delay times, power consumption, size and cost [1.1-1.3].Recently many researchers have tried to develop high speed architectures which are multiplier suitable for VLSI implementation. As of fabrication per transistor on a chip the cost has continually down, parallel algorithms for multiplication become increasingly important. Multiplication algorithms based on different number representations have also been widely investigated.

Depending on the applications there are various approaches to

multiplier design. Almost all DSP functions require a considerable amount of multiplications. Some of these functions require the multiplication to be performed at a faster rate while others concentrate on less hardware and moderate speeds.

The application which aim at hardware simplicity and moderate speeds traditionally use in one form or another [1.4-1.14] the add-shift method for multiplication. For a  $n \times n$ -bit multiplication, the basic add-shift technique adds sequentially, one row at a time, the intermediate result to the next row of partial products in a large 2n-bit accumulator, where the carry is allowed to propagate full-length. The principle is similar to the way one multiplies numbers using pen and paper. This carry propagation, along with (n-1)addition times contribute largely the slow speed. This type of multiplier was most prominently used in the signal processors [1.7, 1.8].These early digital ranged from discrete serial multipliers to a complete integration with other DSP functions onto a single chip.

Some DSP systems employ serial binary representations of signal sequences highly multiplexed serial applications such the in as of telephone voice data signals [1.15,1.16], where processing and the serial approach was found to be efficient in digital filter organization. The need to rapidly perform multiplications on a stream of numbers packed closely in time led to the concept of pipeline multipliers [1.16-1.23]. A form of the basic shift-and-add algorithm was often implemented in the pipeline multipliers [1.17-1.20]. Recent pipeline early multipliers are based on the parallel approach [1.21-1.23] to take advantage of better and cheaper VLSI technology.

It has widely been recognised that the traditional shift-and-add algorithm of multiplication takes time  $O(n^2)$ , where n is the maximum wordlengths of the multiplier and multiplicand. This time can be reduced

by combinatorial parallel techniques, but at the cost of increasing the complexity of the circuitry. However, with rapid advancements of VLSI technology which brought about reduced cost of fabrication per transistor on a chip, parallel techniques have become cheaper and more practical. first introduced Wallace Parallel multipliers were independently by [1.24] and Dadda [1.25]. The architectures proposed were based on a tree of full-adder cells to reduce the initial partial product matrix to operands, which are then summed by fast final adders to obtain the final product. Both Dadda's and Wallace's scheme are optimum in the sense of using a minimum stage of full-adders where the speed is shown as a function of  $O(\log n)$ . Unfortunately, the irregular structure of Wallace's Dadda's especially schemes, for large operand wordlengths research into iterative array multiplier architectures. with the existence and development of an ever sophisticated suite of IC array architectures have led design tools, iterative a more dominant role. In contrast with the partial product reduction techniques of Dadda and Wallace, iterative array multipliers exhibit speeds as a function of O(n). Although they are inherently slower, the advantages of the array approach in terms of hardware regularity and interconnectivity more than outweigh the speed advantage of Wallace's and Dadda's schemes. Usually, multiplier recoding techniques like the modified Booth algorithm [1.30,1.31] fast final adders [1.32,1.33] are employed in monolithic and boost speed. A type of array architecture multipliers to its that is implemented single-chip commonly in practical multipliers is the carry-save-array (CSA) [1.26-1.28]. In fact, architecture the lends itself well to automatic generation layout tools and has actually implemented in silicon compilers [1.29].

A more complete review of parallel multipliers is described in Chapter 2 of the thesis. Also reviewed in this chapter are techniques

based on recoding the multiplier bits and recent work on architectures employing different binary number representations.

#### 1.2. Silicon vs. GaAs

A majority of the digital multipliers that have been reported were implemented in the fast bipolar ECL technology to take advantage of its advanced state of maturity. In view of the many recent advances in IC there tendency to contemplate technologies is a employing alternative technologies improve the multiplication higher-speed to process drastically. Indeed, a fair amount of excitement and attention have been paid to the inherently faster GaAs technology. Some authors have reported impressive speeds at moderate power levels of GaAs multipliers [1.34,1.35].

Significant GaAs - silicon ECL differences were observed in the following areas :

- (i) On-chip gate delay

- (ii) Transistor count

- (iii) gate fan-in and fan-out

Small on-chip gate delays give GaAs an essential edge over silicon for high-performance digital systems. These speed advantages are derived from inherent properties such as higher electron mobility and lower parasitic capacitances.

However, the present practical level of integration of GaAs is at the MSI and LSI level whereas silicon ECL has now reached VLSI Transistor count limitations densities [1.57,1.58]. primarily are due the poor yield of large GaAs chips. At MSI and LSI densities one must therefore ask what advantages can be accrued solely from the on-chip gate delays which are already apparent for GaAs and likely to continue in very high gate densities will the future. since not be

available in the near term. One possible answer to this would be that a logic system could be partitioned into small GaAs chips. But, however, it could be argued that little additional performance beyond that of silicon ECL would be gained with on-chip gate delays of as low as 20ps at even LSI device densities, since the chip-to-chip interconnect delays may remain constant and hence limit system performance.

Low fan-in and fan-out of GaAs gates although not believed to be a permanent characteristic, nevertheless currently introduce constraints not found in silicon. Gate fan-out can generally be increased by using larger transistors, as is done in silicon. However, low gate fan-in is a serious problem, particularly for NAND gates. This is because an increase in the number of inputs to a NAND gate reduces the noise margin, and noise margins are very small in GaAs to begin with. In order to achieve working devices with adequate noise margins, very fine control of circuit parameters is required, and this is not yet easily achieved.

Table 1.1, 1.2 and 1.3 compare several recent speed-power figures and delay times of ring oscillators, memory circuits and 8 x 8-bit array multipliers, respectively of GaAs and silicon ECL compiled from [1.36-1.55].

Some conclusions could be drawn from the tables and from some recent papers on bipolar ECL and GaAs [1.56-1.61]. GaAs HEMT, the fastest GaAs circuit may not be significantly faster than silicon ECL at room temperature eventhough it operates at a much higher speed at 77K. In fact, recent results [1.45] show that the performance of HEMT circuits have been shown to be similar to DCFL at 300K. It may require as much power for near equivalent performance to that of silicon ECL. Although recent papers [1.42,1.53,1.61] have reported impressive speeds of were mainly achieved through high-power consumption complex circuit techniques such as the Buffered- FET logic (BFL). The

| Typical gate<br>delay(ps) | power per<br>gate(mW)   |

|---------------------------|-------------------------|

| 45                        | 0.5                     |

| 12.8                      | 2.5                     |

| 90                        | 0.59                    |

| 42                        | 0.5                     |

|                           | delay(ps)  45  12.8  90 |

Table 1.1. Speed-power of Si bipolar and GaAs ring oscillators.

|                         | Access time<br>(ns) | Total power(W) |

|-------------------------|---------------------|----------------|

| GaAS DCFL (0.5μm, 300K) | 2                   | 0.5            |

| GaAs HEMT (0.5µm, 77K)  | 0.9                 | 0.4            |

| Si ECL (1μm, 300K)      | 1                   | N.A *          |

\*not available

Table 1.2. Speed-power of Si bipolar and GaAs 1K RAM.

|                         | Multiplication time (ns) | Total<br>power(W) |

|-------------------------|--------------------------|-------------------|

| GaAS DCFL (0.5μm, 300K) | 5.2                      | 2.2               |

| GaAs HEMT (0.5μm, 77K)  | N.A.                     | N.A.              |

| Si ECL (1μm, 300K)      | 5.25                     | 1.0               |

Table 1.3. Speed-power of Si bipolar and GaAs 8 x 8-bit array multipliers.

less power-hungry Direct-coupled FET logic (DCFL) have gate delays that are 2 to 4 times those of BFL for complex logic circuits.

Major breakthroughs in terms of gate counts and yield of GaAs chips would therefore need to be achieved before it could be considered as a serious alternative in the implementation of high performance systems. This could be a good number of years to come. On the other hand silicon bipolar technology is continually being improved to achieve and challenge GaAs speeds and it is widely considered as the technology of high speed multipliers for many years to come.

#### 1.3. Research objectives

advent of VLSI technology has undoubtedly permitted The integration of more complex digital functions on to a single chip giving that are more compact, faster and reliable. Indeed, these advantages have prompted the current trend towards single chip realizations of digital signal processors.

As was identified earlier, the main constraint to higher performance of DSP is the multiplication speed. Iterative array multipliers such as the CSA multiplier has often been recognized by IC designers to be most suitable for incorporation in single chip DSPs by virtue of its highly ease of design and expandability for larger operand structure, wordlengths. Although faster multiplication techniques like Dadda's Wallace's schemes. and the of multiplier recoding use techniques are feasible, these normally introduce too much [1.30,1.31] complexity the already complicated DSP and irregularities in design, occupying a larger percentage of the silicon area which should otherwise be taken up by other DSP functions. However, with growing demands for more powerful and real-time performance of single chip DSPs, it is obvious that further improvements in speed would need to be made on iterative arrav

multipliers than that offered by the full-adder CSA architecture.

Dadda first recognized the fact that considerable increases in the speed of parallel multipliers can be achieved by adding more than partial product bit at a time by employing higher order parallel (p,q) counters [1.25]. This approach heavily depends on a counter which has a delay and complexity comparable to that of a full-adder. complicated and irregular wiring between counters of different sizes Dadda's scheme has, however hampered the practical use of this approach high-speed multipliers. More often, serious constraint in large a extending Dadda's technique to higher order parallel counters has been the rather complex and/or slow operation (compared to a full-adder) of such counters. In the last 20 years many researchers have schemes to realise parallel counters with different degrees of success. These include techniques based on two-level gate network [1.62],sequential circuits [1.63,1.64], table look-ups or ROMS [1.65],threshold [1.25,1.66-1.68] and networks of full-adders or smaller logic counters [1.69-1.74].

The aim of this work is to investigate iterative parallel architectures based on higher order counters as opposed to the partial reduction techniques proposed by Dadda, suitable implementation in single chip bipolar DSP applications. The large number of DSP chips that are in the market today are mostly designed in CMOS technology, but with the ever growing demand of real-time performance of DSP applications, especially in image processing, future designs would obviously need to be implemented in the inherently faster bipolar ECL technology. Improved bipolar processes have evolved recently [1.56-1.58] and thus it is appropriate to investigate a more efficient realisation of multipliers in bipolar technology which would ultimately lead powerful, real-time performance single chip digital more signal

processors.

little attention has been paid in the past to iterative In fact. array schemes based on larger counters and thus it is necessary to understand how techniques such as the CSA architecture could be extended. Since the viability of the approach is highly dependent on an efficient implementation of the associated parallel counters, a considerable amount of work is needed to examine various possible configurations of With todays bipolar technology of smaller size counters. and power-hungry transistors [1.56-1.58], a more combinatorial approach realize the counters in order to achieve significant improvements in the multiplication speed should be feasible. Bipolar ECL/EFL circuit techniques and threshold logic, which was shown in the past to efficient in the synthesis of large counters ought to be considered. The work, ultimately includes an examination of the counters inherent speed in contrast with the fastest full-adder design which would then allow a critical comparison of the new array scheme with conventional CSA multipliers.

#### 1.4. Outline of thesis

Chapter 2 reviews the traditional and most commonly used schemes of designing parallel high-speed multipliers. The two main techniques parallel multipliers - the partial product reduction method of Wallace and Dadda, and the iterative CSA architecture are assessed in terms of speed and their attractiveness for VLSI implementation. Also, multiplier recoding techniques and multiplication different based binary on representations are examined. An introduction to the concept of using parallel (p,q) counters to enhance multiplication speed is presented. The require further investigations identified areas that are then and considered.

Chapter 3 describes work undertaken to design a high-speed, bipolar 16 x 16-bit multiplier which was designed in collaboration with Hewlett Packard Company, Santa Clara in the IC design Centre, University College architectures commonly employed in a London. The typical high-speed demonstrated through discussions of the chip. multiplier are Also described is a test chip composed of ring oscillators of full-adder cells made up of different transistor sizes and load resistors. The chip was used to characterize the delay of the full-adder cell in order to get an optimum design of the 16 x 16-bit multiplier and also as the basis of comparison with larger (p,q) counters.

In Chapter 4, extension of the CSA approach and novel multipliers based on higher order parallel (p,q) counters are first studied. An iterative array (5,3) counter multiplier recently reported highlighted and a novel architecture based on similar concepts of (5,3)counter multiplier but employing (2,2,3)counters are then presented. These architectures are assessed in terms of speed their attractiveness for VLSI implementation.

Chapter 5 describes the implementation of the (5,3) counter (2,2,3) counter cells in cascode ECL and threshold logic. The complexity efficiency of operation speed of the two counters using techniques are emphasized. A novel circuit technique which overcomes the needing high fan-in weight earlier problem of threshold presented. A technique of mapping a logic function onto series gated ECL suitable for software implementation is also described.

circuit simulations, Using SPICE a critical examination the propagation delay of the (5,3)counter and (2,2,3)counter implemented in ECL and threshold logic in comparison with a full-adder cell is made in Chapter 6. The novel threshold circuit technique is also maximum fan-in weight. analyzed to characterize its Α gate level

simulation is then performed on the optimum novel array multiplier architecture to evaluate its speed in contrast with conventional CSA multipliers.

Chapter 7 gives a discussion of the conclusions made and identifies areas that require further work.

#### REFERENCES

- [1.1] J.R. Mick & J. Springer, "Single chip multiplier expands digital role in signal processing", Electronics, Vol. 49, pp. 103-108, May 13, 1976.

- [1.2] W. Bucklen, J. Eldon, L. Schirm & F. Williams, "Single-chip digital multipliers form basic DSP building blocks", EDN, PP.153-163, April 1, 1981.

- [1.3] S. Waser & A. Peterson, "Real-time processing gains ground with fast digital multiplier", Electronics, pp. 93-99, Sept. 29, 1977.

- [1.4] E.E. Swartzlander Jr., "The quasi-serial multiplier, "IEEE Trans. Computer, Vol. C-22, No. 4, pp. 317-321, April 1973.

- [1.5] D. Hampel, K.E. Mcguire & K.J. Prost, "CMOS/SOS serial-parallel multiplier", IEEE J. Solid-State Circuits, Vol. SC-11, pp. 669-678, Oct. 1975.

- [1.6] J.R. Verjans, " A serial-parallel multiplier using the NENDEP technology ", IEEE J. Solid-State Circuits, Vol. SC-12, pp. 323-325, June 1977.

- [1.7] N.R. Powell & J.M. Irwin, "A MOS monolithic chip for high-speed flexible FFT processors", IEEE Int. Solid-State Circuits Conf., pp. 18-19, 1975.

- [1.8] N. Ohwada, T. Kimura & M. Doken, "LSI's for digital signal processing", IEEE Trans. on Electron Devices, Vol. ED-26, No. 4, pp. 292-298, 1979.

- [1.9] I. Chen & R. Willoner, "An O(n) parallel multiplier with bit-sequential input and output ", IEEE Trans. Computers, Vol. C-28, No. 10, pp.721-727, Oct. 1979.

- [1.10] R. Gnanasekaran, "On a bit-serial input and bit-serial output multiplier", IEEE Trans. Computers, Vol. C-32, No. 9 pp. 878-880, Sept. 1983.

- [1.11] T. Rhyne & N.R. Strader, " A signed bit-sequential multiplier ", IEEE Trans. Computers, Vol. C-35, No. 10, pp. 896-901, Oct. 1986.

[1.12] N.R. Strader & V.T. Rhyne, "A canonical bit sequential multiplier", IEEE Trans. Computers, Vol. C-31, No. 8, pp. 791-795, August 1982.

- [1.13] J. A. Starzyk & V. S. R. Dandu, "Overlapped multi-bit scanning multiplier", Proc. IEEE ICCD, pp. 363-366, 1985.

- [1.14] R. Gnanasekaran, " A fast serial-parallel binary multiplier ", IEEE Trans. Computers, Vol. C-34, No. 8, pp. 741-744, August 1985.

- [1.15] L.B. Jackson, J.F. Kaiser & H.S. Mcdonald, "An approach to the implementation of digital filters", IEEE Trans. Audio Electroacoust., Vol. AU-16, pp. 413-421, Sept. 1968.

- [1.16] S.L. Freeny, "Special-purpose hardware for digital filtering ", Proc. IEEE, Vol. 63, pp. 633-648, Apr. 1975.

- [1.17] R.F. Lyon, "Two's complement pipeline multipliers", IEEE Trans. Commun., Vol. COM-12, pp. 418-425, April 1976.

- [1.18] J. Kane, "A low-power, bipolar, two's complement serial multiplier chip", IEEE J. Solid-State Circuits, Vol. SC-11, No. 5, pp. 669-678, Oct. 1976.

- [1.19] G. L. Baldwin, "A modular, high-speed serial pipeline multiplier for digital signal processing ", IEEE J. Solid-State Circuits, Vol. SC-13, No. 3, pp. 400-408, June 1978.

- [1.20] E.K. Cheng & C.A. Mead, " A two's complement pipeline multiplier ", IEEE Int. Conf. Acoustics, Speech and signal processing, pp.647-650, 1976.

- [1.21] M. Hatamian & G. L. Cash, " A 70-MHz 8-bit x 8-bit parallel pipelined multiplier in 2.5-um CMOS ", IEEE J. Solid-State Circuits, Vol. SC-21, No. 4, pp. 505-513, August 1986.

- [1.22] T. G. Noll et al, "A pipelined 330-MHz multiplier", IEEE J. Solid-State Circuits, Vol. SC-21, No. 3, pp. 411-416, June 1986.

- [1.23] J. Deverell, "Pipeline iterative arithmetic arrays", IEEE Trans. Computers, pp. 317-322, March 1975.

- [1.24] C.S. Wallace, " A suggestion for parallel multipliers, " IEEE Trans. Electron. Comput. Vol. EC-13, pp 14-17, Feb. 1964.

- [1.25] L. Dadda, "Some schemes for parallel multipliers, "Alta Frequenza, Vol. 34, pp. 349-356, Mar. 1965.

- [1.26] A. Habibi & P.A. Wintz, "Fast Multipliers, "IEEE Trans. Computer, Vol. C-19, pp. 153-157, Feb. 1970.

- [1.27] S. Waser, "High speed monolithic multiplier for real time digital signal processing, "Computer, Vol. 11, no. 10, pp. 19-29, Oct. 1978.

- [1.28] E.L. Braun, Digital Computer Design, New York, Academic Press, 1963.

- [1.29] N.F. Benschop, " Layout compiler for variable array multipliers ",

Proc. Custom Integrated Circuits Conf., pp.47-58, 1983.

- [1.30] D. Booth, "A signed binary multiplication technique, "Quart. J. Mech. Appl. Math., Vol. 4, part 2, 1951.

- [1.31] L.P. Rubinfield, "A proof of the modified Booth's algorithm for multiplication", IEEE Trans. Computers, pp. 1014-1015, Oct. 1975.

- [1.32] J. Sklansky, " An evaluation of several two-summand binary adders ", IRE Trans. Electronic Computers, pp. 213-226, June 1960.

- [1.33] J. Sklansky, "Conditional-sum addition logic ", IRE Trans. Electronic Computers, pp. 226-231, June 1960.

- [1.34] Y. Nakayama, K. Suyama, H. Shimuzu, N. Yokoyama, H. Onishi, A. Shibatomi & H. Ishikawa, "A GaAs 16 x 16 bit parallel multiplier, "IEEE J. Solid-State Circuits, Vol. SC-18, No.5, October 1983.

- [1.35] F.S. Lee, G.R. Kaelin, B.M. Welch, R. Zucca, E. Shen, P. Asbeck, C.P. Lee, C.G. Kirkpatrick, S.I. Long & R.c. Eden, " A high-speed LSI GaAs 8 x 8 bit parallel multiplier, " IEEE J. Solid-State Circuits, Vol. SC-17, no. 4, pp. 638-647, Aug. 1982.

- [1.36] T. Sakai & M. Suzuki, "Super self-aligned bipolar technology", Symp. VLSI technology, Dig. Tech. papers, pp. 16-19, 1983.

- [1.37] R. Ranffit & H. Rein, "High-speed bipolar logic circuits with low power consumption for LSI- A comparison ", IEEE J. Solid-State Circuits, Vol. SC-17, No. 4, pp. 703-712, August 1982.

- [1.38] P.M. Soloman, " A comparison of semiconductor devices for high-speed logic ", Proc. of the IEEE, Vol. 70, No. 5, pp. 489-509, May 1982.

- [1.39] T.H. Ning & D.D. Tang, "Bipolar trends", Proc. of the IEEE, Vol. 74, No. 12, pp. 1669-1677, Dec. 1986.

- [1.40] S. Wiedmann, " Advancements in bipolar VLSI circuits and technologies ", IEEE J. Solid-State Circuits, Vol. SC-19, No. 3, pp. 282-290, June 1984.

- [1.41] J. Lohstroh, "Devices and circuits for bipolar (V)LSI", Proc. of the IEEE, Vol. 69, No. 7, pp. 265-279, July 1981.

- [1.42] V. Milutinovic & D. Fura, "An introduction to GaAs Microprocessor architecture for VLSI, "IEEE Computer, pp.30-42, March 1986.

- [1.43] B.K. Gilbert, "Design and performance trade-offs in the use of Si VLSI and Gallium Arsenide in high clockrate signal processors", IEEE Publication 1984, pp. 260-266.

- [1.44] L. Larson, J. Jensen, P. Greiling & M. Waldner, "GaAs technology for high speed digital computation", IEEE Publication 1985, pp. 384-389.

- [1.45] J.V. DiLorenzo et al, "GaAs Status and directions", IEEE Publication 1985, pp. 371-383.

[1.46] S.I. Long et al, "High speed GaAs integrated circuits", Proc. of the IEEE, Vol. 70, No. 1, pp. 35-45, Jan. 1982.

- [1.47] H. Yuan, "The status and prospect of GaAs bipolar LSI", IEEE Publication 1985, pp. 391-394.

- [1.48] R.C. Eden, "Comparison of GaAs device approaches for ultrahigh-speed VLSI", Proc. of the IEEE, Vol. 70, No. 1, pp. 5-12, Jan. 1982.

- [1.49] R.C. Eden, B.M. Welch, R. Zucca & S.I. Long, "The prospects for ultra high-speed VLSI GaAs digital logic", IEEE J. Solid-Stae Circuits, Vol. SC-14, No.2, pp. 221-239, April 1979.

- [1.50] N. Weste, "GaAs design and simulation issues-are they any different from silicon", IEEE Publication 1984, pp. 268-272.

- [1.51] G. Nuzzilat et al, "GaAs MESFET IC's for gigabit logic applications ", IEEE J. Solid-Stae Circuits, Vol. SC-17, No. 3, pp. 569-583, June 1982.

- [1.52] P.M. Soloman & H. Morkoc, " Modulation-doped GaAs/AlGaAs heterojunction field-effect transistors (MODFET's), ultrahigh-speed device for supercomputers ", IEEE Trans. Electron devices, Vol. ED-31, No. 8, pp. 1015-1027, August 1984.

- [1.53] T.J. Drummond, W.T. Masselink & H. Morkoc, "Modulation-doped GaAs/(Al,Ga) heterojunction field-effect transistors: MODFETs ", Proc. of the IEEE, Vol. 74, No. 6, pp. 773-822, June 1986.

- [1.54] B.M. Welch, R.C. Eden & F.S. Lee, "GaAs digital integrated circuit technology", Chapter 13, Gallium Arsenide, 1985 John Wiley & sons ltd.

- [1.55] Morkoc & P.M. Soloman, "The HEMT: a superfast transistor", IEEE Spectrum, pp. 28-35, Feb. 1984.

- [1.56] K. Washio, T. Nakamura, K. Nakazato & T. Hayashida, " A 48ps ECL in a self-aligned bipolar technology ", Digest of Int. Solid-State Circuits Conf., pp. 58-59, Feb. 1987.

- [1.57] " Fairchild's radical process for building bipolar VLSI ", Electronics, pp. 55-101, Sept. 4 1986.

- [1.58] "Technology to watch, "Electronics, pp. 35-38, April 7, 1986.

- [1.59] Y. Oowaki et al, " A sub-10-ns 16x16 multiplier using 0.6- $\mu$ m CMOS technology ", IEEE J. Solid-State Circuits, Vol. SC-22, No. 5, pp. 762-765, Oct 1987.

- [1.60] Y. Oowaki et al, " A 7.4ns CMOS 16 x 16 multiplier ", Digest of International Solid-State Circuits Conference, pp. 52-53, Feb. 1987.

- [1.61] B.K. Gilbert & G. Pau, "The application of GaAs integrated circuit technology to the design and fabrication of future generation digital signal processors: promises and problems", Proc. of the IEEE, Vol. 76, No. 7, pp. 816-834, July, 1988.

[1.62] E. E. Swartzlander, Jr., "Parallel Counters", IEEE Trans. Computers, Vol. C-22, No. 11, pp. 1021-1024, Nov. 1973.

- [1.63] A. Svoboda, " Adder with distributed control ", IEEE Trans. Computers, Vol. C-19, No. 8, pp. 749-751, August 1970.

- [1.64] S. Singh & R. Waxman, "Multiple operand addition and multiplication", IEEE Trans. Computers, Vol. C-22, No. 2, pp. 113-120, Feb. 1973.

- [1.65] L. Dadda, "On parallel digital multipliers", Alta Frequenza, pp. 574-580, Oct. 1976.

- [1.66] D. Ferrari & R. Stefanelli, "Some new schemes for parallel multipliers, "Alta Frequenza, Vol. 38, pp. 843-852, Nov. 1969.

- [1.67] D.Hampel & R.O. Winder, "Threshold logic ", IEEE Spectrum, pp. 32-39, May 1971.

- [1.68] R.O. Winder, "Threshold logic will cut costs, especially with boosts from LSI", Electronics, pp. 94-103, May 27 1968.

- [1.69] C. C. Foster & F. D. Stockton, "Counting responders in an associative memory", IEEE Trans. Computers, pp. 1580-1583, Dec. 1971.

- [1.70] S. Dormido & M. A. Canto, "Synthesis of generalized parallel counters", IEEE Trans. Computers, Vol. C-30, No. 9, pp. 699-703, September 1981.

- [1.71] H. Kobayashi & H. Ohara, " A synthesizing method for large parallel counters with a network of smaller ones ", IEEE Trans. Computers, Vol. C-27, No. 8, pp. 753-757, August 1978.

- [1.72] S. Dormido & M. A. Canto, "An upper bound for the synthesis of generalized parallel counters", IEEE Trans. Computers, Vol. C-31, No. 8, pp. 802-805, August 1982.

- [1.73] D. G. Gajski, "Parallel Compressors", IEEE Trans. Computers, Vol. C-29, No. 5, pp. 393-398, May 1980.

- [1.74] L. Dadda, "Composite parallel adders", IEEE Trans. Computers, Vol. C-29, No. 10, pp. 942-946, October 1980.

#### **CHAPTER 2**

#### APPROACHES TO PARALLEL MULTIPLIER DESIGN

#### 2.1. Introduction

Digital multipliers continue to occupy a position of major importance in the design and development of general and special purpose computers. As one of the key elements in digital signal processors, the consideration has traditionally hampered the of signal processing owing high cost, poor approach to to speed-power performance and inefficient packaging. Major advances in the realization multipliers monolithic integrated circuits [2.1-2.13] of as have much to reduce delay times, power consumption, size and cost. However, trend towards single chip digital signal processors with the and demand for lower higher speed and increased cost, higher efficiency realizations of digital signal processors [2.14] continued improvements in the performance of digital multipliers is needed.

This chapter reviews the traditional and well-known schemes of designing monolithic high speed, parallel multipliers commonly employed today. The full-adder carry-save array (CSA) [2.15,2.16], Wallace tree algorithm [2.16-2.18], Booth [2.16,2.19,2.20] fast final adders and [2.21-2.24] are described. Multipliers based on the full-adder CSA those that employ the Booth algorithm and fast final adders are assessed in terms of the two main criteria - speed and complexity. The key areas that require further investigations are then identified and considered.

Complexity is defined in the context of high-speed multipliers as a measure of how regular the architecture is in terms of layout and how attractive it is for VLSI implementation. The speed of a multiplier is conventionally taken to be the worst case delay, which is the maximum

number of gate delays that a propagating signal could traverse in the architecture, although on average, the computations take less time.

#### 2.2. Traditional approaches to multiplier design

In the development of monolithic high-speed multipliers the classic, add-and-shift algorithm [2.16] has been superseded by more parallel approach to multiplier design. The rapid development and advancement of IC technology over the past twenty years has made the fabrication of parallel multipliers become economically more feasible and parallel encouraged many researchers to look at algorithms [2.1-2.13,2.15-2.18,2.34-2.53] and those based on different binary number representations [2.8,2.53-2.58] which suitable for **VLSI** are implementation.

be done in either signed or unsigned Multiplication can From the arithmetic and implementation point of view, two's complement is the most attractive for signed numbers. Addition is straight-forward and significantly faster than sign-and-magnitude say, and multiplication is easier to understand and implement. Two's complement has often been stated in the past to be difficult due to the correction with negative need for sign operands. However, this from the days of expensive logic and since hangover then many 'correction' algorithms reported [2.42-2.47]. The have been full-adder [2.33] has always been the basic cell used for the implementation of multipliers. Irrespective of technology parallel the used. the is easy to design and the associated architectures are simple and regular which makes them ideal for VLSI.

There are three basic methods that have been developed over the years to improve the speed of the simple add-and-shift multiplier. The

the addition of partial products by using speeds up parallel parallel multiplication architectures. Schemes for are roughly divisible iterative into classesarray of cells [2.1-2.13,2.15,2.16,2.34-2.47] two generation of a matrix of partial product terms with subsequent reduction of of the matrix by means parallel counters [2.16-2.18,2.25-2.28,2.48-2.51]. The second reduces the number of rows of partial products by employing multiplier recoding techniques [2.29] like modified Booth algorithm [2.19,2.20]. Lastly fast adders [2.21-2.24] often used at the last stage to add up the final two rows of sum-carry pairs.

For the purpose of simple illustration, examples of 5 x 5-bit multiplication are given; also dot representation (where each dot is a binary bit) of the partial products is used.

#### 2.2.1. Parallel multiplication schemes

Multiplication is a special case of many consecutive Under these circumstances it is not necessary to let the carry signals propagate until all the partial products have been added. Each full adder bit is a three input device, with two outputs. Thus if these two outputs fed to two of the three inputs of appropriately weighted bit are positions for the next addition, a new partial product can be added via the third input. This type of adder is also known as a Carry Save Adder since the carry is saved and not propagated. A basic carry-save array (CSA) multiplier is shown in Figure 2.1 for a 5 x 5-bit multiplier where array of these adders are appropriately connected. All the partial products are formed simultaneously, added and shifted appropriately by hardware. Lower significant final product bits up to P<sub>n-1</sub> i.e. the final product bit of weight 2<sup>n-1</sup> are generated automatically by the right-most

1

Figure 2.1 Block diagram of a 5 x 5- bit multiplier using carry-save technique [2.15].

column cells whilst the higher significant final product bits are computed by an extra stage of full-adders at the bottom of the array.

For an n x n bit multiplication the array requires 1 stage of half adders and (n-1) stages of full adders. The worst-case delay (including the AND gate delay for the generation of partial product bits) is given by

since the longest carry propagate chain in the array is through the right column and bottom edge of the array. Thus this architecture employs one cell for the main multiplication array, and with the regularity, modularity simple interconnections between adders, is and ideal from a

VLSI implementation point of view.

Additional speed can be gained by the use of a Wallace tree [2.15-2.18] which is a form of matrix generation-reduction scheme. In series of full-adders, this architecture. a that operate in parallel. combines groups of three bits of the same binary weight to produce a vector of Sum bits (S) and a vector of Carry bits (C). If more than one C and one S vectors are generated from the first stage, these are combined again in groups of three in the next stage. This procedure continues until one C and one S vector remain. Then a string of full-adders is applied to those two vectors to obtain the final result. In general, for a n x n-bit multiplication the number of gate delays necessary to reduce n partial products to one C and one S vector is given [2.16] by

$$\left[\begin{array}{cc} \log \frac{3}{2} & n \\ \end{array}\right] - 1 \tag{2.2}$$

Figure 2.2 shows a block diagram of a Wallace tree for the multiplication of 5-bit numbers in the ideal case where all bits of the same binary weight are under the same column. However, unless a large chip area is used, this is not the case in an actual design. In a minimum area layout, bits of the same binary weight are in different columns, and additional wiring is required for the interconnection of the appropriate products resulting in a much more complex and irregular interconnection pattern.

Dadda [2.25-2.26] also introduced a similar procedure to the Wallace tree for reducing the partial products to two numbers using full-adders. His procedure is optimum in the sense that it uses a minimum number of full-adders. The difference between this technique and Wallace's scheme is in their ways of connecting full adders.

Comparisons between the three architectures on the basis of speed

Figure 2.2. Block diagram of a 5 x 5-bit multiplier using Wallace's scheme [2.15].

and complexity are discussed in section 2.2.4

#### 2.2.2. Fewer partial products

Another speed-up technique called Booth's algorithm [2.19],increases speed by reducing the number of partial products by half; this reduces the number of carry-save adder stages, and hence the total It multiplication delay. requires little hardware without also substantially increasing the complexity of the main multiplication array.

Basically, Booth's algorithm allows the multiplication operation to skip over any contiguous strings of all 1s and all 0s, rather than form a partial product for each bit. Skipping a string of 0s is straightforward, but in skipping over a string of 1s, the following property is put to use: a string of 1s can be evaluated by subtracting the weight of the rightmost 1 from the modulus. Thus, the value of the string 11100 computes to  $2^5-2^2 = 28$ . However, in Booth's algorithm consecutive strings

of 3-bits of the multiplier word are recoded with the most significant bit of the string saved for the next higher string to enable us to remember the previous action. All possible permutations are computed from Table 2.1. The algorithm works for two's complement numbers and requires that the multiplier be padded with a 0 to the right of the least significant bit (LSB) to detect the start of a string of 1s. To work with unsigned numbers the multiplier must also be padded with 0s to the left of the MSB so that the multiplier will not be treated as a negative number.

| Y <sub>i+1</sub>                | Yi                                   | Y <sub>i-1</sub>                | Oper a tion                                                                                                                                       |

|---------------------------------|--------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>0<br>0<br>0<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0 | Add zero Add multiplicand Add multiplicand Add 2x multiplicand Subtract 2x multiplicand Subtract multiplicand Subtract multiplicand Subtract zero |

All operations are followed by a 2-bit shift.

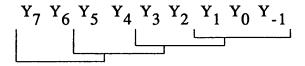

Breaking a 8-bit multiplier into five groups of 3 bits each:

Table 2.1. A modified Booth algorithm.

Although one could take and decode more than 3 bits at a time, the Booth encoder required becomes more complicated and impractical as a vector of three times the multiplicand would need to be generated and this cannot be easily obtained by simple shifting of the partial product.

A full-propagate addition is needed to generate this, limiting the effectiveness of the reduction in the number of carry-save additions.

#### 2.2.3. Fast final adders

If we look at the straight full-adder CSA, Wallace and Dadda tree there is a vector of sum and carry bits (also known as the Intermediate Product [IP] bits) being added by a string of full-adders in order to significant product bits. However, the final higher the IΡ would have settled down to their final values after a gate delay given by number of stages of full-adders. The string of full-adders the basically a ripple-carry adder [2.21] and though is ideal for **VLSI** implementation, it is slow due to rippling of the carry bit. Thus, the addition of significant IP is of the higher bits one the main speed-limiting factor of the CSA multiplier and thus calls for a faster adder architectures than the simple ripple carry adder.

Conventional fast adders can be roughly categorized into 2 of algorithms. conditional-sum and carry-look-ahead [2.21]. Conditional-sum was invented by Sklansky [2.21,2.22] and it has been considered by Winograd [2.30] to be faster than the carry-look-ahead. This was evaluated based on an (r,d) circuit, which is a d-valued logical circuit in which each element has a fan-in at most r and can compute any r-argument, d-valued logical function in unit time. Table 2.2. [2.21-2.24,2.77] shows the comparisons of addition speed (in gate delays) architectures with the theoretical lower bound given of the two Winograd. Other fast adder architectures have been reported over the like the canonic and Ling [2.59] adders but are limited by implementation problems.

From an implementation point of view, the conditional sum adder is

|                       | Gate delays                                           |

|-----------------------|-------------------------------------------------------|

| Winograds lower bound | log <sub>r</sub> 2n                                   |

| Carry-look-ahead      | $4 \left[ \log_{\mathbf{r}} \mathbf{n} \right]$       |

| Conditional - s um    | $2 + \log_r + \left\lceil \frac{n-r}{r} \right\rceil$ |

Table 2.2. Relative speeds of fast adder architectures

more attractive because of its more regular and simpler layout compared to the carry-look ahead. Furthermore, the carry-look ahead is plagued by high gate fan-in and fan-out requirements for large operand wordlength. The conditional-sum adder is thus the most attractive scheme both in speed and layout. For a much faster addition, a combination of these two types of adders could be employed if the area overhead and power requirements are tolerable. In fact, Winograd showed that with an (r,d) the theoretical lower bound (fastest time) of addition of circuit. two achievable with conditional-sum operands is nearly the and carry-look-ahead combination algorithm.

### 2.2.4. Architectural comparisons

The procedure for the reduction of the partial products is the basic difference between the CSA array, Wallace's and Dadda's schemes. Wallace's Dadda's schemes, the number of stages increases as the and logarithm of n whereas in the carry save scheme the number of stages is linearly dependent equations on n as shown in (2.2)and (2.1),respectively. Thus Dadda's and Wallace's techniques are much faster than the CSA array for large wordlength n. Both Dadda's and the CSA array approach are optimum in the sense of using a minimum number of full adders. Wallace's scheme usually needs more full adders.

In general, matrix generation-reduction schemes are much faster than array types since their speed of operation increases with the logarithm of the wordlength [2.16,2.17]. The array schemes, however are more ideal for VLSI implementation because of their regular layout and use of one basic circuit type. The rather complicated and irregular wiring between the adders in a Wallace tree has often hampered their practical use in high-speed, single chip multipliers.

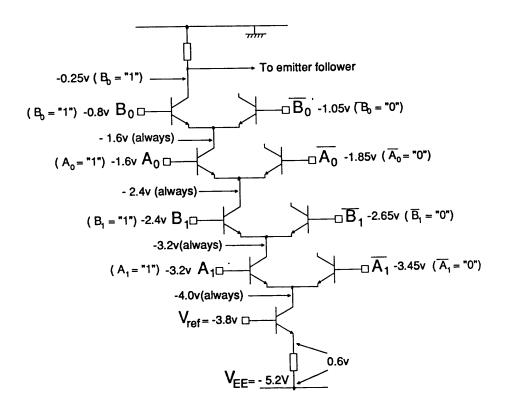

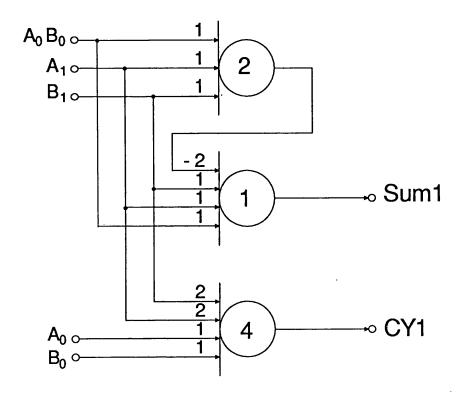

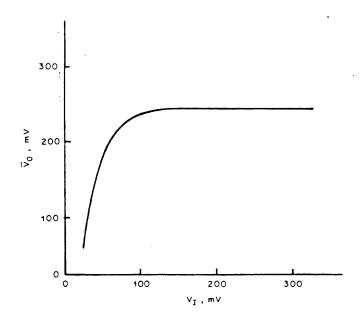

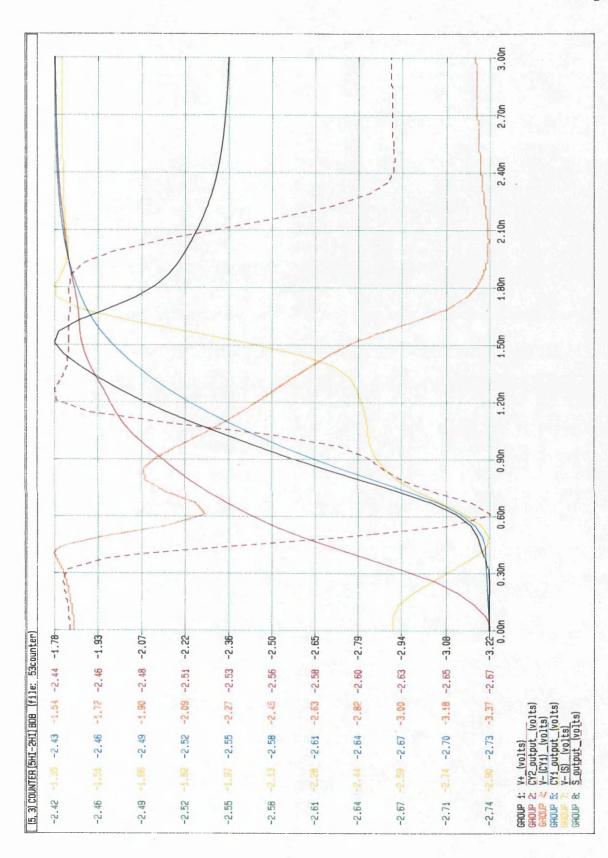

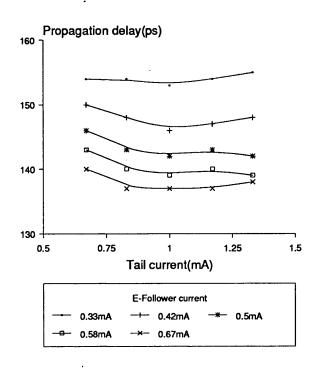

Thus, for large multipliers like a 32 x 32-bit, the advantages of array in terms of hardware regularity and interconnectivity the CSA outweigh speed advantage of the Wallace architecture. the tree array architecture is easily expandable by adding Furthermore, the CSA additional rows and columns of full adders to fit the application. However, if the Booth encoder is to be employed in the design this must be accompanied by the use of a fast final adder. Without a fast adder the speed of the multiplier is not significantly better than that of the straight CSA since the critical path for both schemes is along the right column and bottom row of full-adders where the final product bits are computed.