# Towards the integration of InP photonics with silicon electronics: design and technology challenges

W. Yao, *Member, IEEE*, X. Liu, *Student Member, IEEE*, M. Matters-Kammerer, *Member, IEEE*, A. Meighan, M. Spiegelberg, *Student Member, IEEE*, M. Trajkovic, *Member, IEEE*, J.J.G.M. van der Tol, M. J. Wale, *Member, IEEE*, X. Zhang, K. A. Williams, *Member, IEEE*

Abstract—Intimate integration of photonics with electronics is regarded as the key to further improvement in bandwidth, speed and energy efficiency of information transport systems. Here, a method based on wafer-scale polymer bonding is reviewed which is compatible with foundry-sourced high-performance InP photonics and BiCMOS electronics. We address challenges with respect to circuit architecture, co-simulation framework and interconnect technology and introduce our approach that can lead to broadband high-density interconnects between photonics and electronics. Recent proof-of-concept work utilizing DC-coupled driver connections to modulators, which significantly reduces the interconnect complexity, is summarized. Furthermore, cosimulation concepts based on equivalent circuit models are discussed with emphasis on the importance of impedance matching between driver and modulator. Finally, realizations of broadband interconnects and functional photonic building blocks after wafer bonding are highlighted to demonstrate the potential of this wafer-scale co-integration method.

Index Terms—Photonic integrated circuits, wafer scale integration, BiCMOS integrated circuits, optical transceiver, electronic photonic integration

#### I. INTRODUCTION

THE motivation to integrate photonic functionality with electronic circuits has been long-lasting [1]. Electronic Integrated Circuits (EIC) followed Moore's Law scaling to reach today's state-of-the-art billion transistor chips, capable of Teraflops of data processing [2]. Photonic Integrated Circuits (PIC) are undergoing a similar progression, driven by the exponential increase in capacity demand of information transport systems, reaching thousands of components and terabit/s on chip [3], [4]. In both cases continued advances in the level of integration and the laws of scaling have been fundamental in meeting the communication and processing needs of today's applications.

However, with information systems pressing for higher performance and requiring further reduction of cost and power consumption, continued scaling of EIC and PIC separately from each other falls short to keep up with the demand. This can be attributed to the shortcomings of the current technology used to interconnect electronics and photonics, which failed to scale at the same pace and lacks the required bandwidth density in Tb/s

per unit area. It poses a significant bottleneck to the performance of combined electronic-photonic systems, especially visible in data transport applications ranging from medium distance links to optical interconnects in data centers, on-board optics and chip-to-chip communications. It has been predicted for example that high-speed transceiver interface scaling will not be able to keep up with future increases in data generation and processing in ASICS, if current scaling rates are to continue [5]. To overcome this disparity, the photonic part of the transceiver has to be brought as close as possible to the electronics using co-integration approaches. Furthermore, coherent systems are now being used more frequently in short optical links, as well as in longer-haul systems, and these depend on complex, fast electronics to be closely interfaced with optical modulators and detectors, once again necessitating a higher degree of co-integration [6]. Likewise, the growth in channel count for Gigabit ethernet [7] and Tb/s optical interconnects [8] demands parallel scaling of connections between electronics and photonics for increased capacity, whereas the increase in symbol rate dictates close integration of the two in order to reduce electrical parasitics and enlarge serial bandwidth. A clear demand thus arises for scaling electronics and photonics as a co-integrated system incorporating highdensity broadband interconnects and move towards convergence of the two.

Several technological approaches are being followed to realize this ambition. Monolithic concepts create photonic functionality on top of mature electronic processes with zero change e.g. in BiCMOS [9], CMOS [10] or InP [11]. This has led to transmitters and receivers reaching 64 GBaud operation in BiCMOS [12], [13], [14], albeit obtained with limited analog bandwidth (18 GHz for the modulator and 34 GHz for the receiver), and the realization of CMOS chiplets for chip-to-chip communications (13 GHz modulator, 5 GHz receiver) [10] [15]. Those examples show great promise with respect to integration density and scalability, but compromise on the optical circuit performance compared to dedicated photonic processes.

Dedicated silicon photonic foundry processes are well established and allow for higher overall transmit and receive

performance [10] than their monolithic CMOS and BiCMOS counterparts, but laser integration remains to be a challenge for all silicon platforms and subject of active research. Generic InP based foundries in contrast can readily integrate active materials [16]-[18], rely on a stronger electro-optic (EO) Kerr and Pockels effect and thus achieve higher EO bandwidthefficiency metrics [19]. Further enhancement of the EO effect can be accomplished with the quantum-confined Stark effect in quantum wells, but at the cost of higher temperature and wavelength dependence. Modulators and detectors with bandwidths exceeding 80 GHz have been demonstrated using the InP material system [20], [21], which, together with the capability for monolithic integration of various types of laser circuits [22], [23], makes InP PICs very attractive for cointegration with EICs. On the electronics side, generic foundry processes such as the 0.25 µm BiCMOS technology have been found to be well suited for high-speed transmitter and receiver front-ends [24]-[26]. A second approach to advance towards electronic-photonic convergence is therefore to rely on foundry-sourced high-performance EICs and PICs and cointegrate them using a scalable high-density interconnect process. The advantage is that well established electronic and photonic technology can be used essentially without change and thus without compromising the commercial foundry model or the performance of the combined system. The key challenge in this approach lies in establishing a scalable high-performance integration technology between electronics and photonics with high-speed interconnects.

Conventional co-packaging concepts connect highly integrated electronics with densely packed photonics using wire bonds that run along the edge of the circuits [3]. These introduce significant parasitics, causing signal degradations [27] and, more profoundly, only allow a limited number of connections due to the one-dimensional nature of the interface. Stud bump bonding used in flip-chip assemblies supports broadband connections and provides a two-dimensional interface [28], [29]. This has been applied on die level and used successfully to connect high-speed DACs and drivers to EAM arrays and to terminate MZMs with resistive load chips [20], [30]. However, wafer-level packaging is preferred in industry for scalability reasons, as it can enable lower production cost and higher yield [31], [32]. Die-to-wafer and wafer-to-wafer bonding are two promising approaches here. We pursued the latter for its potential to achieve higher throughput and the possibility to define interconnects between electronics and photonics lithographically at fine resolution, going beyond what current die-level processes can achieve in density and size.

Wafer bonding using polymers such as BCB as the adhesive layer has been suggested as a promising wafer-level technology to integrate electronics and photonics [33]. It is compatible with foundry sourced high-performance wafers, scalable in process and can be applied in a mature production environment [34]. Here we pursue this approach and discuss several challenges that need to be tackled on the route to electronic-photonic convergence.

Currently, the interconnect schemes between EIC and PIC are designed to operate with cumbersome and bulky biasing and

supply circuitry, not suitable for high-density wafer-scale bonding. Innovations in circuit architecture and coupling schemes are needed that facilitate direct connection of driver electronics with fast optics. Furthermore, co-design and cosimulation becomes much more important in optimizing and predicting the combined system performance once EIC and PIC are closely integrated. New methodologies that incorporate electronic and photonic device models are needed. Finally, realizing broadband, high-density electrical interconnects through the polymer bonding layer is a key technology challenge to successful co-integration. In this paper, we present the recent work of the authors related to these design and technology aspects, extending the material presented in [35], and discuss how advances here can lead to wafer-scale cointegration of photonics with electronics. Section II discusses the interconnect schemes that are required for direct connection of EIC and PIC. Section III summarizes a joint electronic photonic simulation framework based on equivalent circuit representations and section IV outlines the progress in developing a high-density interconnect technology that supports broadband operation. Results of proof-of-concept building block operation will be presented and the conclusion is given finally in section V.

# II. INTERCONNECTION SCHEME BETWEEN ELECTRONICS AND PHOTONICS

## A. Interconnect Complexity

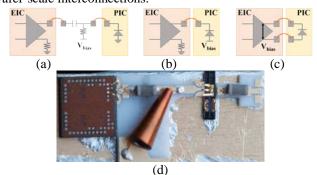

Most modulator and detector devices require a DC bias to operate at their optimum. This is usually fed through a biasing circuit (AC coupling) which requires an external bias source and is inserted between the EIC and PIC as shown in Figure 1a for a driver-modulator configuration. When co-packaging devices, it can be easily realized in combination with wire bonds and surface mount components as depicted in Figure 1d. However, when moving towards two-dimensional wafer-scale interconnections with a high degree of integration, such a biasing circuit is not desired as the connection needs to be kept as short as possible to increase the achievable density and reduce parasitics. A direct connection between the driver output and modulator input is needed (DC coupling), as indicated in Figure 1b, c for the single-ended and differential case, respectively. Appropriate driver designs that support DC coupling reduce the coupling complexity and thus enable wafer-scale interconnections.

Figure 1: Connection between EIC and PIC using (a) biasing circuit and AC coupling, (b) single-ended DC coupling and (c) differential DC coupling. (d) Assembly of EIC and PIC using AC coupling.

#### B. DC Coupling Proof-of-Concept

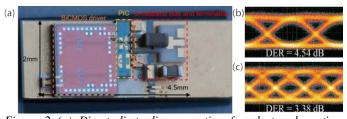

The single-ended DC coupling scheme has been used to connect drivers with electro-absorption modulators (EAM) [36] We have designed and fabricated a driver with DC coupling in a commercial 0.25 µm SiGe:C BiCMOS foundry technology, exhibiting 31.5 GHz bandwidth, 3V p-p output swing and open electrical eye diagrams at 56 Gb/s PAM-4 (VEC of 9.98 dB), leading to 6.5 pJ/bit power consumption [37]. The operation speed and energy per bit of the driver is limited by the transit frequency available on the commercial process but is sufficient for a proof-of-concept for DC coupling to photonics. To demonstrate the feasibility of a simplified interconnection with the modulator, we have paired it with EAM devices with 32 GHz of bandwidth [38] which were manufactured in a generic InP photonic foundry [39]. The DC coupling scheme was demonstrated with wire bond chip-to-chip interconnection to verify the operation of the scheme, as shown in Figure 2a. Note that the complexity of the connections between EIC and PIC in Figure 2a has reduced to a few direct bonds compared to Figure 1d. In principle, the termination loads on the right-hand side of the EAM can be integrated into the EIC when moving towards wafer-scale integration. The assembly has been characterized in transmission experiments with results and further details given in [40]. It exhibits open optical eye diagrams with an extinction ratio of 3.38 dB at 36 Gb/s NRZ, verifying the DC coupling operation [40]. The wire bonds are the limiting factor in this experiment, as both the driver and EAM had been characterized separately to work at higher modulation speeds.

Figure 2 (a) Direct die-to-die connection for electro-absorption modulator-driver combination enabled through DC coupling with eye diagrams at (b) 20Gbit/s and (c) 36Gbit/s NRZ modulation. [40]

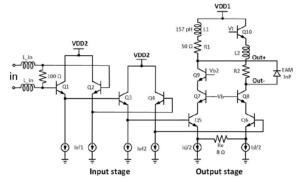

The single-ended DC coupling only makes use of half the available driver output swing voltage. In contrast, differential DC coupling can utilize the complete output swing with reduced common mode distortion and has been suggested in [41]. We have previously reported a novel driver design, shown in Figure 3, which is based on differential DC coupling that utilizes an asymmetric load configuration to provide up to -2V of bias for EAMs [24]. It can also operate in single-ended drive and allows for two EAMs to be connected with separate bias adjustments. It has been fabricated in the same commercial 0.25 um SiGe:C BiCMOS foundry technology, exhibiting 51.5 GHz bandwidth, 2V p-p output swing and open electrical eye diagrams at 56 Gb/s PAM-4 (VEC of 10 dB), leading to 3.9 pJ/bit power consumption [24]. Most recently we have assembled the drivers with EAM modulators using the cointegration technology presented in section IV. The validation experiments are presently in progress.

Figure 3: Driver with differential output and asymmetric load [24].

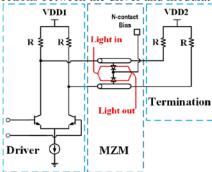

Similarly, for connecting to Mach-Zehnder modulators (MZM), DC coupling can reduce the complexity of the interconnection, as demonstrated in [42], [43]. Such a connection scheme is shown in Figure 4. Here, the data signal can be fed from the differential driver directly to the electrodes of the MZM and passed to a termination circuit at the output side. The modulator bias voltage is provided through the driver output with respect to the n-contact point of the photonic chip. This is possible if the MZM is made on semi-insulating substrate and operated in series push-pull [44], enabling short direct connections between the driver and modulator.

Figure 4: Circuit diagram of driver-MZM connection with termination.

We have designed a MZM driver based on a five-stage distributed amplifier topology that works with differential DC coupling and differential termination. It can supply 4 V p-p swing, exhibiting a bandwidth of 40 GHz, and was manufactured in the 0.25 µm SiGe:C BiCMOS technology [45]. To verify the DC-coupled operation, it has been combined with a DBR-laser-MZM transmitter that was fabricated in an experimental generic photonic foundry run [46]. The travellingwave MZM, capable of 40 Gb/s NRZ operation with 35 GHz of bandwidth [47], is connected to the driver and to a resistor load chip which is fabricated in the same BiCMOS technology. The bias voltage is applied through the MZM n-contact. Wire bonds are used again to form an assembly of EIC and PIC to verify the working principle. We could observe open large-signal optical eve diagrams for the assembly at 30 Gb/s NRZ (extinction ratio of 5.63 dB), which validates the DC coupling scheme for driver-MZM assemblies. In the experiment, the modulator output is loaded with a 50 Ohm resistor, matching the MZM characteristic impedance. However, the driver output is intended for 100 Ohm differential output and its performance is degraded due to a mismatch to the MZM impedance. In

principle, with the ability to co-design the EIC and PIC, any other value of impedance can be targeted and further performance improvement can be expected. Here, the focus lies on the DC-coupled interconnection scheme but we will see in section III that proper impedance matching between driver and modulator has a significant impact on the system performance.

#### C. Bond Wire Performance

The two assemblies using bond wires clearly illustrate that adopting a DC coupling scheme reduces the complexity of the interconnects between EIC and PIC by omitting otherwise cumbersome biasing circuitry. This is a prerequisite when moving towards wafer-scale co-integration processes. Furthermore, it becomes clear that the wire bonds are a limiting factor with respect to speed. Transitioning from high inductance wire bonds towards stud bump bonding and ultimately to wafer-scale interconnects will increase the bandwidth and density of connections that can be pushed through the interface.

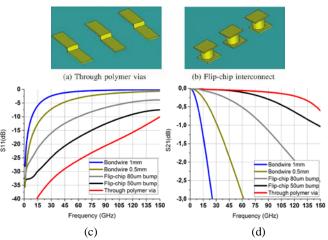

Figure 5: 3D model of (a) 40 µm wide and 7 µm high TPV and (b) 50 µm diameter stud bump connections. Simulated (c) S11 and (d) S21 for bond wire, stud bump and TPV connections. [48]

We have modeled bond wires, stud bump and through polymer via (TPV) interconnects in Advanced Design System (ADS) [49] using the standard bond wire model [50] and CST Studio Suite [51] with custom geometries. Figure 5a,b depict the shape of 40 µm wide, 7 µm high TPVs and stud bumps with 40 μm height and either 50 μm or 80 μm diameter in a coplanar GSG configuration. We performed simulations in [48] to compare their respective bandwidths with that of standard wire bonds, 0.5 and 1 mm in length, 25 µm in diameter, and the results are shown in Figure 5c,d. It can be seen that moving from wire bonds to stud bumps significantly improves the bandwidth, which is attributed to the omission of wire inductance and a reduction in interconnect resistance. Although well-designed short ribbon bonds can be of high bandwidth and alleviate some of the wire bond drawbacks, they do not provide the needed level of interconnect density. Further improvement in bandwidth can be achieved when moving to TPVs, with only 0.5 dB transmission loss at 150 GHz. This is due to their smaller dimensions and less parasitic pad capacitances compared to the stud bump case.

This section has presented ways to simplify the interconnect circuitry between EIC and PIC, particularly for high-speed transmitters, and demonstrated these techniques using die-to-die assemblies. The schemes we have presented become essential for wafer-scale co-integration using TPV interconnects, which have been shown in simulation to perform much better than conventional wire and stud bump bonding.

#### III. CO-SIMULATION AND DESIGN FRAMEWORK

Another challenge when moving towards co-integrated electronic and photonic systems is to predict the performance of the combined system accurately. This can be achieved when the simulation approaches and design flows for the EIC and for the PIC are consolidated. Recent work has focused on integrating compact models of photonic devices into standard CMOS simulation environments e.g. using VerilogA [52], [53] or with commercial links between software providers such as Cadence and Lumerical establishing common electronic photonic design automation (EPDA) [54]. It works well for passive optics that can be described with S-parameters but becomes more challenging when modelling active components such as lasers or modulators in combination with driver electronics [55]. Especially for high-speed applications, it is important to correctly capture and account for the RF chain between the driver, interconnects and modulator.

We summarize our work on developing an equivalent circuit based electro-optic model for a MZM device that can be easily implemented in electronic tools to be co-simulated with driver models. This is illustrated in an example where the modulator is connected with an electrical filter circuit.

#### A. Electrical Model of Modulators

A successful model of the MZM for co-simulation purposes needs on the one hand to be simple to implement in electronic circuit simulation environments such as ADS or Cadence Spectre, whilst on the other hand also capture the physical mechanisms that govern the modulator operation such as transmission line effects, voltage induced refractive index change and the optical interferometer transfer function.

Figure 6: Equivalent circuit model for traveling-wave MZM modulator.

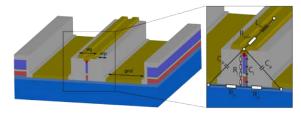

We are using a combination of an equivalent circuit model with analytical first-principle calculations to represent electrical signal propagation along the optical phase modulator, capturing the interplay between the transmission line and the optical wave. Figure 6 illustrates the cross-section of a coplanar MZM electrode and how the equivalent circuit is mapped to the electrode geometry. Each element is calculated from first principles through analytical expressions that depend on the design geometries. It is further resolved spatially by constructing a distributed equivalent circuit along the

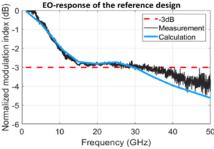

propagation direction to incorporate the effect of travelingwave behavior and electrical signal to optical group velocity mismatch. The voltage dependent refractive index change along the modulator electrode is calculated by incorporating the Pockels, Kerr and plasma dispersion effects in the optical waveguide. The model is implemented within the ADS tool [49] and allows for structural optimization which directly results in changes in the output of a system simulation and has been verified against experimental small and large-signal measurements of manufactured InP traveling-wave MZMs [56]. This allowed the current limitations to modulator speed to be analyzed and has yielded 100 GHz class optimized modulator designs [57]. Figure 7 shows a good match of the calculated electro-optic frequency response from our model with the measured data for a modulator device used for calibration purposes. Here, the fast reduction and plateau of the EO response is due to an impedance mismatch of the electrode (~25  $\Omega$ ) to the measurement environment (50  $\Omega$ ). The model successfully accounts for mismatch effects which will be discussed in the next section and agrees with the experimental data.

Figure 7: Calculated EO frequency response compared with measured data of 1 mm long traveling-wave coplanar MZM for model calibration [56].

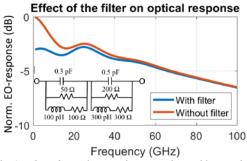

To illustrate that the model can easily be extended to interface with electronic circuits, we connect the modulator to an electrical filter as shown in the inset of Figure 8. In this case, its purpose is to pre-emphasize the analog signals entering the modulator electrode and achieve a flatter overall frequency response, which can be seen in Figure 8. Similarly, this approach can be extended to incorporate a complete driver circuit and used for co-simulation of EIC and PIC performance.

Figure 8: Combined simulation of pre-emphasis filter with modulator model indicating a flattening of frequency response.

#### B. Choice of Impedances

Co-integrating drivers and modulators on wafer-scale eliminates lengthy cabling and connections between them. Thus, the need to match to the standard RF system impedance of 50 Ohm is no longer present and the value of driver output

and modulator load impedances can instead be chosen freely to optimize for low power consumption or high-speed operation.

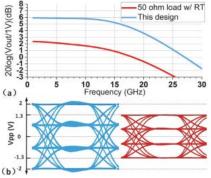

Instead of using 50 Ohm load resistors in the output driver stage, resistors with 40 Ohm can be implemented in combination with inductors of 166 pH, with the latter responsible for an inductive peaking effect in the frequency response [37]. This peaking can compensate for EAM losses and achieve a higher bandwidth in the driver-EAM system overall. Furthermore, it results in higher voltage gain in the driver and higher output swing as shown in Figure 9.

Figure 9: Simulated driver performance with different loading configurations: (a) voltage gain vs frequency and (b) eye diagram at 20 GBaud PAM-4.[37]

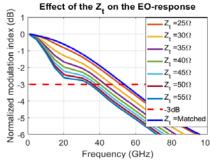

Similarly, the loading condition at the end of the modulator device is an important parameter that can be optimized. If the driver modulator interface is already impedance matched, the modulator loading can also deviate from 50 Ohm and take a value that maximizes the bandwidth. Utilizing the equivalent circuit model, we have analyzed this on MZM electrodes, for which the electro-optic modulation index has been calculated for different load resistor values [56], illustrated in Figure 10. In this case, the characteristic impedance of the modulator has the value of 23 Ohm, causing a better broadband match if the load is between 20 and 25 Ohm. It can be seen that the bandwidth increases significantly over the 50 Ohm loading case from 35 GHz to 60 GHz.

Both examples illustrate the importance of a joint approach to EIC and PIC simulation and show how an equivalent circuit model can help analyze the role of impedance matching on the total driver-modulator performance.

Figure 10: Simulated modulation index vs frequency for varying loading conditions [56].  $Z_t$  is the termination load value.

#### IV. Co-Integration Technology

Next to the interconnect circuit schemes and the co-simulation framework, the development of wafer-scale interconnection technology is central in achieving electronic-photonic cointegration and increasing density. The wafer bonding process is one part of it, but also the realization of broadband metal connections in the form of through-polymer vias is essential for connecting contact pads between the electronic layer and photonic layer.

### A. Wafer Bonding Process

Several wafer bonding techniques exist and have been studied in the literature [58]. We pursue adhesive wafer bonding here, as it has been successfully applied to bond InP devices on silicon wafers for heterogeneous integration schemes [59], using BCB as a bonding polymer. It allows for moderately low bonding temperatures and low levels of outgassing, being used widely in 3D packaging of electronic ICs [60], [61].

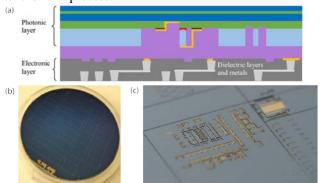

Within the WIPE [62] project, the BCB bonding process has been developed to work with fully populated electronic and photonic wafers, accommodating total vertical topology variations up to 9 µm. The bonding scheme is illustrated in Figure 11a, with further details reported in [63]. The BCB is spin-coated onto both wafers and then soft-baked. The actual bonding is performed at a temperature of 240°C, which is limited by the used BiCMOS technology. Temperature budget tests have been performed to define the boundary conditions. For 15~hours at 240°C no degradation has been detected, while 1~hour at 280°C resulted in measurable performance reduction. The photonic wafer and electronic wafer are bonded facing each other to enable the shortest possible electrical connections. The BCB is cured for 10~hours to guarantee full cross linking according to [64], [65].

The alignment is performed using the backside alignment technique [34]. Markers on the backside of the InP wafer are transferred by optical contact lithography. The theoretical wafer-to-wafer alignment accuracy is 2 µm. We have tested wafer bonds with varying BCB thicknesses and observed reproducible accuracy <4 µm. This is sufficiently small to realize broadband high-density interconnects between the EIC and PIC. The InP and silicon wafer have a different linear thermal expansion coefficients (CTEs) which will result in a shift during bonding. This position dependent effect can be precalculated and compensated for during the design phase of the InP wafer. It has further no influence on the overall alignment. Finally, the substrate of the InP wafer is removed in a wet etch step until only the functional photonic layers remain. Figure 11 (b), (c) show a bonded sample of a 3" InP photonic wafer on top of a silicon electronic BiCMOS wafer and the contact pads after the TPV process.

Figure 11: (a) Illustration of PIC bonded to EIC [63]. (b) Microphotograph of bonded photonic wafer on electronic wafer. (c) Microphotograph of EIC and PIC after TPV creation.

#### B. Through Polymer Via Interconnects

After a successful bond, the interconnections need to be established. The developed TPV process has been reported in [66]. To create vias, the photonic layers and the BCB bonding layer at the positions of the InP and BiCMOS contact pads are completely removed in an etching step, so that they are exposed. To define sloped side walls in the BCB-layer, on which the metal interconnects can be created, a photoresist AZ9260-layer [67] is used in combination with reactive ion etching. For the via metallization, a seed layer of Ti/Au is applied, followed by an electro-plating process. The schematic of the via process and SEM images of realized TPVs can be seen in Figure 12 and Figure 13.

Figure 12: Illustration of through polymer vias created between EIC and PIC.

Figure 13 Through polymer vias with a) completed process module showing top-to-bottom-surface electrode connection b) one via with dimensions  $116 \times 116 \, \mu m^2$  and c) detailed view of the via.[66]

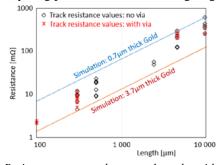

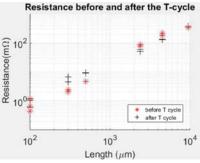

These TPVs have been characterized in both DC and RF measurements, in order to assess their suitability for broadband interconnects in high-speed applications. For the DC measurement, we have established TPVs through 7 µm thick BCB. Figure 14 shows the resistance obtained in a four-probe measurement on tracks of different lengths that either contain a via transition or not [66]. It can be seen that the resistance values follow the predicted length dependence. No significant difference is caused due to a via transition compared to tracks without vias. Since the thickness of the TPV metal varies as a result of the used plating process, upper and lower resistance estimates have been calculated and plotted. The minimum TPV size depends on the thickness of the bonding layer and can be reduced to be similar in dimension. Given a good wafer planarity, it can be reduced to the order of ~10 µm, making them suitable for high-density connections. Further tests shown in Figure 15 reveal that the measured resistance before and after a temperature cycling procedure does not change significantly.

Figure 14: Resistance measured on metal tracks with and without TPVs at different track lengths. [66]

Figure 15: Measured DC resistance of TPVs before and after temperature cycling (-40°C to 85°C, 15 min dwell time, 400 cycles).

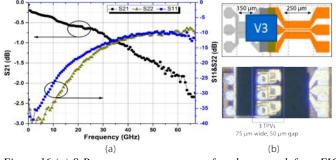

For the RF characterization, we have formed TPVs through 24 µm thick BCB, connecting coplanar waveguide tracks on an InP sample with tracks on a BiCMOS wafer [68]. A thicker bonding layer is utilized here to cover the increased wafer topology. S-Parameter values measured from the EIC to the PIC are shown in Figure 16. It is worth noting that transmission lines on both sides are not de-embedded in this case and their influence is included in the measured results. The S21 of the coplanar tracks including three TPV transitions of 75 µm width and 50 µm separation lies above -3dB within the full measurement range until 67 GHz. The reflection values are kept below -10 dB until 50 GHz, confirming that TPVs can act as broadband RF interconnects between EIC and PICs. Note that the measurement includes the effect of the transmission line losses on both the EIC and PIC side and higher bandwidth for the pure TPV structures can be expected after de-embedding of the transmission lines. Further improvement can be gained by shrinking the dimensions of the TPV structures.

Figure 16 (a) S-Parameter measurement of coplanar track from EIC to PIC that contains TPVs (75  $\mu$ m wide, 50  $\mu$ m gap). (b) Schematic and microphotograph of test structure.

# C. Photonic building blocks

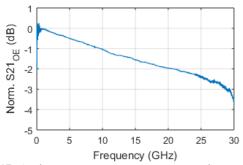

To validate the TPV technology in combination with the adhesive polymer bonding approach for functional device building blocks, we have performed bonding experiments with foundry-sourced wafers [68]. An electronic wafer is fabricated in the NXP SiGe 0.25µm BiCMOS technology and contains transmitter and receiver components. Section II has presented connection schemes that were implemented in the EIC designs. The photonic wafer originates from the HHI generic InP foundry platform [16], [17], [69], which has been used to produce PICs for a wide range of applications ranging from optical transceivers [70] to circuits for optical signal processing [71]. We designed Tx and Rx building blocks on the photonic wafer in form of DFB lasers with EAMs and PIN photodiodes with spot-size converters (SSC), respectively. The photonic and

electronic wafers have been bonded and dies cut out from the full wafers. We report the performance of the photonic building blocks after bonding and the TPV process. The key component for the receiver is the pin photodiode. Its 3dB OE bandwidth after wafer bonding has been measured to reach 28 GHz as shown in Figure 17. The exact device could not be measured before bonding to avoid surface damage but typical bandwidth values are around 35 GHz. We assume that the degradation is linked to reflections from the SSC but more investigation is needed to explain the reduced bandwidth.

Figure 17: OE frequency response measurement of PIN photodetector building block after wafer bonding.

On the transmitter side, thermal dissipation becomes a challenge. The lasers are operated uncooled and initial DFB laser measurements with 4  $\mu s$  current pulses at 100 mA with a 1 kHz duty cycle lead to laser operation at -4 dBm output power collected in fibre. It can also be pumped up to cw current of 35 mA and achieves -13 dBm optical power in fiber. Advanced heat extraction schemes from both the EIC and PIC are topics of ongoing research. Losses between the optical waveguide and the fibre are estimated at 6 dB in these preliminary measurements. The performance of the co-integrated transmitter and receiver circuits still needs to be characterized.

#### V. CONCLUSION

A wafer-scale approach for co-integration of photonics with electronics is presented in this paper, which promises to overcome the interconnect bottleneck of current wire or stud bump bonding techniques and establish broadband, highdensity connectivity between PIC and EIC. Several challenges with respect to the interconnection scheme, the co-simulation framework and the technological realization are addressed and recent work on these aspects is reviewed. DC coupled drivermodulator connections reduce the interconnect complexity and are essential for wafer-scale co-integration. A circuit-based modelling framework is discussed that enables co-simulation of PIC and EIC so that impedance and equalization can be optimised. The proposed co-integration technology is based on polymer wafer bonding and subsequent TPV creation, which allows the combination of high-performance foundry photonics with foundry electronics. We have demonstrated its feasibility by creating 67 GHz TPV interconnects and verifying the operation of bonded photonic laser and detector building blocks. In light of on-going improvements in foundry photonics [16], [18] and the emergence of nanophotonic platforms [72] combined with faster electronic capabilities, we regard the proposed wafer-scale co-integration approach as an important step towards electronic photonic convergence.

# ACKNOWLEDGEMENT

The authors would like to thank F. Soares and M. Baier from the Fraunhofer Heinrich-Hertz Institute for fruitful discussions and manufacturing of the photonic samples. Prof. Domine Leenaerts is thanked for his valuable inputs and supporting the production of the BiCMOS drivers at NXP Semiconductor. Tim Durrant from Effect Photonics is thanked for the temperature cycle experiments. This work has received funding from the EU H2020 programme under grant agreement No. 688572 (WIPE), from the EU-project GeTPIC, from the Dutch research agency NWO through the HTSM Photronics project and from the Dutch Stimulus OPZuid programme through the OpenPICs project.

#### REFERENCES

- [1] O. Wada, T. Sakurai, and T. Nakagami, "Recent progress in optoelectric integrated circuits (OEIC's)," *IEEE J. Quantum Electron.*, vol. 22, no. 6, pp. 805–821, Jun. 1986, doi: 10.1109/JQE.1986.1073053.

- [2] S. Markidis, S. W. D. Chien, E. Laure, I. B. Peng, and J. S. Vetter, "NVIDIA Tensor Core Programmability, Performance Precision," in 2018 IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW), May 2018, pp. 522–531, doi: 10.1109/IPDPSW.2018.00091.

- [3] F. Kish et al., "System-on-Chip Photonic Integrated Circuits," IEEE J. Sel. Top. Quantum Electron., vol. 24, no. 1, pp. 1–20, Jan. 2018, doi: 10.1109/JSTOE.2017.2717863.

- [4] M. Smit, J. van der Tol, and M. Hill, "Moore's law in photonics," *Laser Photonics Rev.*, vol. 6, no. 1, pp. 1–13, Jan. 2012, doi: 10.1002/lpor.201100001.

- [5] P. J. Winzer and D. T. Neilson, "From Scaling Disparities to Integrated Parallelism: A Decathlon for a Decade," *J. Light. Technol.*, vol. 35, no. 5, pp. 1099–1115, Mar. 2017, doi: 10.1109/JLT.2017.2662082.

- [6] H. Yamazaki et al., "Digital-Preprocessed Analog-Multiplexed DAC for Ultrawideband Multilevel Transmitter," J. Light. Technol., vol. 34, no. 7, pp. 1579–1584, Apr. 2016, doi: 10.1109/JLT.2015.2508040.

- [7] "IEEE P802.3bs 400 Gb/s Ethernet Task Force." http://www.ieee802.org/3/bs/ (accessed Jul. 28, 2020).

- [8] H. Nasu, K. Nagashima, T. Uemura, A. Izawa, and Y. Ishikawa, ">1.3-Tb/s VCSEL-Based On-Board Parallel-Optical Transceiver Module for High-Density Optical Interconnects," *J. Light. Technol.*, vol. 36, no. 2, pp. 159–167, Jan. 2018, doi: 10.1109/JLT.2017.2766081.

- [9] D. Knoll et al., "BiCMOS silicon photonics platform for fabrication of high-bandwidth electronic-photonic integrated circuits," in 2016 IEEE 16th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF), Jan. 2016, pp. 46–49, doi: 10.1109/SIRF.2016.7445464.

- [10] V. Stojanović et al., "Monolithic silicon-photonic platforms in state-of-the-art CMOS SOI processes [Invited]," Opt. Express, vol. 26, no. 10, p. 13106, May 2018, doi: 10.1364/OE.26.013106.

- [11] J.-K. Park, S. Takagi, and M. Takenaka, "Monolithic integration of InGaAsP MZI modulator and InGaAs driver MOSFET using III-V CMOS photonics," in 2017 Optical Fiber Communications Conference and Exhibition (OFC), Mar. 2017, pp. 1–3.

- [12] G. R. Mehrpoor et al., "64-GBd DP-Bipolar-8ASK Transmission Over 120 km SSMF Employing a Monolithically Integrated Driver and MZM in 0.25-µm SiGe BiCMOS Technology," in 2019 Optical Fiber Communications Conference and Exhibition (OFC), Mar. 2019, pp. 1–3

- [13] S. Gudyriev et al., "Coherent ePIC Receiver for 64 GBaud QPSK in 0.25 μm Photonic BiCMOS Technology," J. Light. Technol., vol. 37, no. 1, pp. 103–109, Jan. 2019, doi: 10.1109/JLT.2018.2881107.

- [14] B. Wohlfeil et al., "First Demonstration of Fully Integrated Segmented Driver and MZM in 0.25-µm SiGe BiCMOS employing 112 Gb/s PAM4 over 60 km SSMF," in 2018 European Conference on Optical Communication (ECOC), Sep. 2018, pp. 1–3, doi: 10.1109/ECOC.2018.8535510.

- [15] M. Wade et al., "TeraPHY: A Chiplet Technology for Low-Power, High-Bandwidth In-Package Optical I/O," IEEE Micro, vol. 40, no. 2, pp. 63–71, Mar. 2020, doi: 10.1109/MM.2020.2976067.

- [16] F. M. Soares et al., "High-Performance InP PIC Technology Development based on a Generic Photonic Integration Foundry," in 2018 Optical Fiber Communications Conference and Exposition (OFC), Mar. 2018, pp. 1–3.

- [17] M. Liehr et al., "Chapter 4 Foundry capabilities for photonic integrated circuits," in Optical Fiber Telecommunications VII, A. E. Willner, Ed. Academic Press, 2020, pp. 143–193.

- [18] G. E. Hoefler et al., "Foundry Development of System-On-Chip InP-Based Photonic Integrated Circuits," IEEE J. Sel. Top. Quantum Electron., vol. 25, no. 5, pp. 1–17, Sep. 2019, doi: 10.1109/JSTQE.2019.2906270.

- [19] K. Liu, C. R. Ye, S. Khan, and V. J. Sorger, "Review and perspective on ultrafast wavelength-size electro-optic modulators," *Laser Photonics Rev.*, vol. 9, no. 2, pp. 172–194, Mar. 2015, doi: 10.1002/lpor.201400219.

- [20] Y. Ogiso *et al.*, "80-GHz Bandwidth and 1.5-V Vπ InP-Based IQ Modulator," *J. Light. Technol.*, vol. 38, no. 2, pp. 249–255, Jan. 2020, doi: 10.1109/JLT.2019.2924671.

- [21] H.-G. Bach et al., "InP-based waveguide-integrated photodetector with 100-GHz bandwidth," IEEE J. Sel. Top. Quantum Electron., vol. 10, no. 4, pp. 668–672, Jul. 2004, doi: 10.1109/JSTQE.2004.831510.

- [22] F. Soares et al., "155nm-span multi-wavelength DFB laser array fabricated by selective area growth," in 2016 Compound Semiconductor Week (CSW) [Includes 28th International Conference on Indium Phosphide Related Materials (IPRM) 43rd International Symposium on Compound Semiconductors (ISCS), Jun. 2016, pp. 1–2, doi: 10.1109/ICIPRM.2016.7528541.

- [23] S. Latkowski, K. A. Williams, and E. a. J. M. Bente, "Monolithically integrated laser sources for applications beyond telecommunications," in *Physics and Simulation of Optoelectronic Devices XXVIII*, Mar. 2020, vol. 11274, p. 112741N, doi: 10.1117/12.2552784.

- [24] X. Zhang, X. Liu, M. Spiegelberg, A. R. van Dommele, and M. K. Matters-Kammerer, "A DC-51.5 GHz Electro-Absorption Modulator Driver with Tunable Differential DC Coupling for 3D Wafer Scale Packaging," 2019 IEEE BiCMOS Compd. Semicond. Integr. Circuits Technol. Symp. BCICTS, p. 4.

- [25] J. Lambrecht et al., "A 106-Gb/s PAM-4 Silicon Optical Receiver," IEEE Photonics Technol. Lett., vol. 31, no. 7, pp. 505–508, Apr. 2019, doi: 10.1109/LPT.2019.2899147.

- [26] H. Ramon et al., "70 Gb/s 0.87 pJ/bit GeSi EAM Driver in 55 nm SiGe BiCMOS," in 2018 European Conference on Optical Communication (ECOC), Sep. 2018, pp. 1–3, doi: 10.1109/ECOC.2018.8535467.

- [27] T. Krems, W. Haydl, H. Massler, and J. Rudiger, "Millimeter-wave performance of chip interconnections using wire bonding and flip chip," in 1996 IEEE MTT-S International Microwave Symposium Digest, Jun. 1996, vol. 1, pp. 247–250 vol.1, doi: 10.1109/MWSYM.1996.508504.

- [28] R. W. Going et al., "1.00 (0.88) Tb/s per Wave Capable Coherent Multi-Channel Transmitter (Receiver) InP-Based PICs With Hybrid Integrated SiGe Electronics," *IEEE J. Quantum Electron.*, vol. 54, no. 4, pp. 1–10, Aug. 2018, doi: 10.1109/JQE.2018.2840081.

- [29] G. Baumann, D. Ferling, and H. Richter, "Comparison of flip chip and wire bond interconnections and the technology evaluation on 51 GHz transceiver modules," in 1996 26th European Microwave Conference, Sep. 1996, vol. 1, pp. 98–100, doi: 10.1109/EUMA.1996.337527.

- [30] S. Kanazawa et al., "214-Gbit/s 4-PAM operation of flip-chip interconnection EADFB laser module," J. Light. Technol., vol. PP, no. 99, pp. 1–1, 2016, doi: 10.1109/JLT.2016.2632164.

- [31] P. Pieters, "Wafer level packaging of micro/nanosystems," in 5th IEEE Conference on Nanotechnology, 2005., Jul. 2005, pp. 130–133 vol. 1, doi: 10.1109/NANO.2005.1500710.

- [32] P. Garrou, "Wafer level chip scale packaging (WL-CSP): an overview," IEEE Trans. Adv. Packag., vol. 23, no. 2, pp. 198–205, May 2000, doi: 10.1109/6040.846634.

- [33] J. J. G. M. van der Tol *et al.*, "Indium Phosphide Integrated Photonics in Membranes," *IEEE J. Sel. Top. Quantum Electron.*, vol. 24, no. 1, pp. 1–9, Jan. 2018, doi: 10.1109/JSTQE.2017.2772786.

- [34] F. Niklaus, G. Stemme, J.-Q. Lu, and R. J. Gutmann, "Adhesive wafer bonding," *J. Appl. Phys.*, vol. 99, no. 3, p. 031101, Feb. 2006, doi: 10.1063/1.2168512.

- [35] K. A. Williams et al., "Indium Phosphide Photonic Circuits on Silicon Electronics," in 2020 Optical Fiber Communications Conference and Exhibition (OFC), Mar. 2020, pp. 1–3.

- [36] J. Verbrugghe et al., "Multichannel 25 Gb/s Low-Power Driver and Transimpedance Amplifier Integrated Circuits for 100 Gb/s Optical

- Links," *J. Light. Technol.*, vol. 32, no. 16, pp. 2877–2885, Aug. 2014, doi: 10.1109/JLT.2014.2319112.

- [37] X. Zhang, X. Liu, A. R. van Dommele, and M. K. Matters-Kammerer, "Dual-Channel 56 Gb/s PAM-4 Electro-Absorption Modulator Driver for 3D Wafer Scale Packaging," in 2018 Asia-Pacific Microwave Conference (APMC), Nov. 2018, pp. 237–239, doi: 10.23919/APMC.2018.8617323.

- [38] M. Trajkovic et al., "64Gb/s Electro Absorption Modulator Operation in InP-Based Active-Passive Generic Integration Platform," in 2018 European Conference on Optical Communication (ECOC), Sep. 2018, pp. 1–3, doi: 10.1109/ECOC.2018.8535339.

- [39] L. M. Augustin et al., "InP-Based Generic Foundry Platform for Photonic Integrated Circuits," IEEE J. Sel. Top. Quantum Electron., vol. 24, no. 1, pp. 1–10, Jan. 2018, doi: 10.1109/JSTQE.2017.2720967.

- [40] M. Trajkovic et al., "36 Gb/s operation of a BiCMOS driver and InP EAM using foundry platforms," in 45th European Conference on Optical Communication (ECOC 2019), Sep. 2019, pp. 1–3, doi: 10.1049/cp.2019.1081.

- [41] H. Ramon et al., "70 Gb/s Low-Power DC-Coupled NRZ Differential Electro-Absorption Modulator Driver in 55 nm SiGe BiCMOS," J. Light. Technol., vol. 37, no. 5, pp. 1504–1514, Mar. 2019, doi: 10.1109/JLT.2019.2900192.

- [42] K. Li et al., "Co-Design of Electronics and Photonics Components for Silicon Photonics Transmitters," in 2018 European Conference on Optical Communication (ECOC), Sep. 2018, pp. 1–3, doi: 10.1109/ECOC.2018.8535212.

- [43] X. Liu, X. Zhang, D. Leenaerts, and M. Matters-Kammerer, "A 100 Gb/s DC-coupled Optical Modulator Driver for 3D Photonic Electronic Wafer-scale Packaging," presented at the IEEE International Symposium on Circuits and Systems (ISCAS), May 2020.

- [44] R. G. Walker, "High-speed III-V semiconductor intensity modulators," IEEE J. Quantum Electron., vol. 27, no. 3, pp. 654–667, Mar. 1991, doi: 10.1109/3.81374.

- [45] X. Liu, X. Zhang, R. van Dommele, H. Gao, D. Leenaerts, and M. K. Matters-Kammerer, "A DC to 40 GHZ 4-VPP Output High-Efficiency Linear Driver for Optical Communication," in 2018 Asia-Pacific Microwave Conference (APMC), Nov. 2018, pp. 1519–1521, doi: 10.23919/APMC.2018.8617463.

- [46] W. Yao, M. K. Smit, and M. J. Wale, "Monolithic 300 Gb/s Parallel Transmitter in InP-Based Generic Photonic Integration Technology," *IEEE J. Sel. Top. Quantum Electron.*, vol. 24, no. 1, pp. 1–11, Jan. 2018, doi: 10.1109/JSTQE.2017.2762602.

- [47] W. Yao, M. K. Smit, and M. J. Wale, "Monolithically Integrated 40 Gbit/s Tunable Transmitter in an Experimental Generic Foundry Process for Large-Scale Integration," in ECOC 2016; 42nd European Conference on Optical Communication, Sep. 2016, pp. 1–3.

- [48] X. Zhang, X. Liu, M. Spiegelberg, A. Meighan, J. J. G. M. van der Tol, and M. K. Matters-Kammerer, "A 50 Gb/s PAM-4 Optical Modulator Driver for 3D Photonic Electronic Wafer Scale Packaging," in 2018 18th Mediterranean Microwave Symposium (MMS), Oct. 2018, pp. 112–115, doi: 10.1109/MMS.2018.8611895.

- [49] "Keysight Technologies Advanced System Design (ADS)." http://www.keysight.com/ (accessed Jul. 30, 2020).

- [50] "BONDW1 to BONDW50 (Philips-TU Delft Bondwires Model) -Keysight Knowledge Center." https://edadocs.software.keysight.com/pages/viewpage.action?pageId =5909161 (accessed Oct. 25, 2020).

- [51] "Dassault Systemes CST Studio Suite." https://www.3ds.com/de/produkte-und-services/simulia/produkte/cststudio-suite/ (accessed Jul. 30, 2020).

- [52] C. Sorace-Agaskar, J. Leu, M. R. Watts, and V. Stojanovic, "Electro-optical co-simulation for integrated CMOS photonic circuits with VerilogA," *Opt. Express*, vol. 23, no. 21, pp. 27180–27203, Oct. 2015, doi: 10.1364/OE.23.027180.

- [53] M. J. Shawon and V. Saxena, "Rapid Simulation of Photonic Integrated Circuits using Verilog-A Compact Models," in 2019 IEEE 62nd International Midwest Symposium on Circuits and Systems (MWSCAS), Aug. 2019, pp. 424–427, doi: 10.1109/MWSCAS.2019.8885372.

- [54] J. Pond, X. Wang, Z. Lu, E. Schelew, G. Lamant, and A. Farsaei, "Latest Advancements to the Industry-Leading EPDA Design Flow for Silicon Photonics: Invited Paper," in 2019 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), Nov. 2019, pp. 1–6, doi: 10.1109/ICCAD45719.2019.8942039.

- [55] J. Pond, G. S. C. Lamant, and R. Goldman, "Chapter 5 Software tools for integrated photonics," in *Optical Fiber Telecommunications VII*, A. E. Willner, Ed. Academic Press, 2020, pp. 195–231.

- [56] A. Meighan, W. Yao, M. Wale, and K. Williams, "Microwave model for optimizing electro-optical modulation response of the Mach-Zehnder modulator," presented at the European Conference on Integrated Optics (ECIO), 2020.

- [57] A. Meighan, W. Yao, M. Wale, and K. Williams, "Design of 100 GHzclass Mach-Zehnder modulators in a generic indium phosphide platform," presented at the IEEE Photonics Conference (IPC), 2020.

- [58] S. H. Lee, K.-N. Chen, and J. J.-Q. Lu, "Wafer-to-Wafer Alignment for Three-Dimensional Integration: A Review," J. Microelectromechanical Syst., vol. 20, no. 4, pp. 885–898, Aug. 2011, doi: 10.1109/JMEMS.2011.2148161.

- [59] S. Stankovic, R. Jones, M. N. Sysak, J. M. Heck, G. Roelkens, and D. Van Thourhout, "1310-nm Hybrid III–V/Si Fabry–Pérot Laser Based on Adhesive Bonding," *IEEE Photonics Technol. Lett.*, vol. 23, no. 23, pp. 1781–1783, Dec. 2011, doi: 10.1109/LPT.2011.2169397.

- [60] A. Jourdain, H. Ziad, P. De Moor, and H. A. C. Tilmans, "Wafer-scale 0-level packaging of (RF-)MEMS devices using BCB," in *Symposium* on *Design*, Test, Integration and Packaging of MEMS/MOEMS 2003., May 2003, pp. 239–244, doi: 10.1109/DTIP.2003.1287044.

- [61] S. Seok, N. Rolland, and P.-A. Rolland, "A Novel Zero-Level Packaging using BCB Adhesive Bonding and Glass Wet-Etching for Millimeter-Wave Applications," in TRANSDUCERS 2007 - 2007 International Solid-State Sensors, Actuators and Microsystems Conference, Jun. 2007, pp. 2099–2102, doi: 10.1109/SENSOR.2007.4300579.

- [62] EU H2020 Project, "Wafer Scale Integration of Photonics and Electronics (WIPE)." http://cordis.europa.eu/project/rcn/199492\_en.html (accessed Jul. 28, 2020).

- [63] M. Spiegelberg, J. van Engelen, T. de Vries, K. Williams, and J. van der Tol, "BCB bonding of high topology 3 inch InP and BiCMOS wafers for integrated optical transceivers," in *Proceedings Symposium IEEE Photonics Society Benelux*, 2018, Brussels, Belgium, Nov. 2018, pp. 160–163.

- [64] The Dow Chemical Company, "CYCLOTENE 3000 Series Advanced Electronic Resins." Feb. 2005.

- [65] P. E. Garrou et al., "Rapid thermal curing of BCB dielectric," in 1992 Proceedings 42nd Electronic Components Technology Conference, May 1992, pp. 770–775, doi: 10.1109/ECTC.1992.204292.

- [66] A. Meighan, M. J. Wale, and K. A. Williams, "Low resistance metal interconnection for direct wafer bonding of electronic to photonic ICs," presented at the Proceedings of the 22nd Annual Symposium of the IEEE Photonics Society Benelux Chapter, Delft, Nov. 2017.

- [67] "AZ® 9200 Photoresist." Product Data Sheet, Accessed: Jul. 30, 2020.

[Online]. Available: https://www.microchemicals.com/micro/tds\_az\_9200\_series.pdf.

- [68] M. Spiegelberg, J. P. van Engelen, K. A. Williams, and J. J. G. M. van der Tol, "Wafer scale technology to integrate photonics on BiCMOS electronics," presented at the IEEE Photonics Benelux Chapter Annual Symposium 2019, Amsterdam, The Netherlands.

- [69] F. M. Soares, M. Baier, T. Gaertner, D. Franke, M. Moehrle, and N. Grote, "Development of a versatile InP-based photonic platform based on Butt-Joint integration," in 2015 11th Conference on Lasers and Electro-Optics Pacific Rim (CLEO-PR), Aug. 2015, vol. 2, pp. 1–2, doi: 10.1109/CLEOPR.2015.7376063.

- [70] N. Andriolli, P. Velha, M. Chiesa, A. Trifiletti, and G. Contestabile, "A Directly Modulated Multiwavelength Transmitter Monolithically Integrated on InP," *IEEE J. Sel. Top. Quantum Electron.*, vol. 24, no. 1, pp. 1–6, Jan. 2018, doi: 10.1109/JSTQE.2017.2746002.

- [71] H.-T. Peng *et al.*, "Temporal Information Processing With an Integrated Laser Neuron," *IEEE J. Sel. Top. Quantum Electron.*, vol. 26, no. 1, pp. 1–9, Jan. 2020, doi: 10.1109/JSTQE.2019.2927582.

- [72] Y. Jiao et al., "Indium Phosphide Membrane Nanophotonic Integrated Circuits on Silicon," Phys. Status Solidi A, vol. 217, no. 3, p. 1900606, 2020, doi: 10.1002/pssa.201900606.