# Don't Sit on the Fence: A Static Analysis Approach to Automatic Fence Insertion

JADE ALGLAVE, Microsoft Research, University College London DANIEL KROENING, University of Oxford VINCENT NIMAL, Microsoft Research DANIEL POETZL, University of Oxford

Modern architectures rely on memory fences to prevent undesired weakenings of memory consistency. As the fences' semantics may be subtle, the automation of their placement is highly desirable. But precise methods for restoring consistency do not scale to deployed systems code. We choose to trade some precision for genuine scalability: our technique is suitable for large code bases. We implement it in our new musketeer tool, and report experiments on more than 700 executables from packages found in Debian GNU/Linux 7.1, including memcached with about 10,000 LoC.

### 1. INTRODUCTION

Concurrent programs are hard to design and implement, especially when running on multiprocessor architectures. Multiprocessors implement weak memory models, which feature, e.g., instruction reordering and store buffering (both appearing on x86), or store atomicity relaxation (a particularity of Power and ARM). Hence, multiprocessors allow more behaviours than Lamport's Sequential Consistency (SC) [Lamport 1979], a theoretical model where the execution of a program corresponds to an interleaving of the operations executed by the different threads. This has a dramatic effect on programmers, most of whom learned to program with SC.

Fortunately, architectures provide special *fence* (or *barrier*) instructions to prevent certain behaviours. Yet both the questions of *where* and *how* to insert fences are contentious, as fences are architecture-specific and expensive in terms of runtime.

Attempts at automatically placing fences include Visual Studio 2013, which offers an option to guarantee acquire/release semantics (we study the performance impact of this policy in Section 2). The C++11 standard provides an elaborate API for inter-thread communication, giving the programmer some control over which fences are used, and where. But the use of such APIs might be a hard task, even for expert programmers. For example, Norris and Demsky [2013] reported a bug found in a published C11 implementation of a work-stealing queue.

We address here the question of how to *synthesise* fences, i.e., how to automatically place them in a program to enforce robustness/stability [Bouajjani et al. 2011; Alglave and Maranget 2011], which implies SC. This should lighten the programmer's burden. The fence synthesis tool needs to be based on a precise model of weak memory. In verification, models commonly adopt an *operational* style, where an execution is an interleaving of transitions accessing the memory (as in SC). To address weaker architectures, the models are augmented with buffers and queues that implement the

This work is supported by SRC 2269.002, EPSRC H017585/1 and ERC 280053.

Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies show this notice on the first page or initial screen of a display along with the full citation. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, to redistribute to lists, or to use any component of this work in other works requires prior specific permission and/or a fee. Permissions may be requested from Publications Dept., ACM, Inc., 2 Penn Plaza, Suite 701, New York, NY 10121-0701 USA, fax +1 (212) 869-0481, or permissions@acm.org.

© YYYY ACM 0164-0925/YYYY/01-ARTA \$15.00 DOI: http://dx.doi.org/10.1145/0000000.0000000 A:2 J. Alglave et al.

features of the hardware. Similarly, a good fraction of the fence synthesis methods, e.g., Linden and Wolper [2013], Kuperstein et al. [2010], Kuperstein et al. [2011], Liu et al. [2012], Abdulla et al. [2013], and Bouajjani et al. [2013] rely on operational models to describe executions of programs.

Challenges. Methods using operational models inherit the limitations of methods based on interleavings, e.g., the "severely limited scalability", as Liu et al. [2012] put it. Indeed, none of them scale to programs with more than a few hundred lines of code, due to the very large number of executions a program can have. Another impediment to scalability is that these methods establish if there is a need for fences by exploring the executions of a program one by one.

Finally, considering models like Power or ARM makes the problem significantly more difficult. Intel x86 offers only one fence (mfence), but Power offers a variety of synchronisation mechanisms: fences (e.g., sync and lwsync) and dependencies (address, data, or control). This diversity makes the optimisation more subtle: one cannot simply minimise the number of fences, but rather has to consider the costs of the different synchronisation mechanisms; for instance, it might be cheaper to use one full fence than four dependencies.

*Our approach*. We tackle these challenges with a static approach. Our choice of model almost mandates this approach: we rely on the axiomatic semantics of Alglave et al. [2010]. We feel that an axiomatic semantics is an invitation to build abstract objects that embrace all the executions of a program.

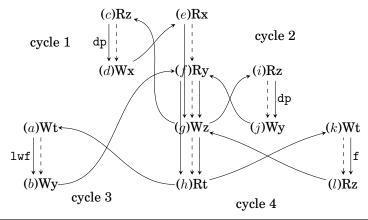

Previous works, e.g., [Shasha and Snir 1988; Alglave and Maranget 2011; Bouajjani et al. 2011; Bouajjani et al. 2013], show that weak memory behaviours boil down to the presence of certain cycles, called *critical cycles*, in the executions of the program. A critical cycle essentially represents a minimal violation of SC, and thus indicates where to place fences to restore SC. We detect these cycles statically, by exploring an over-approximation of the executions of the program.

*Contributions.* We describe below the contributions of our paper:

- A self-contained introduction to axiomatic memory models, including a detailed account of the special shapes of critical cycles (Section 4).

- —A fence inference approach, based on finding critical cycles in the abstract event graph (aeg) of a program (Section 5), and then computing via a novel integer linear programming formulation a minimal set of fences to guarantee sequential consistency (Section 6). The approach takes into account the different costs of fences, and is sound for a wide range of architectures, including x86-TSO, Power, and ARM.

- The first formal description of the construction of aegs (Section 5.4), and a correctness proof showing that the aeg does capture all potential executions of the analysed program (Section 5.5). This includes a description of how to correctly use overapproximate points-to information during the construction of the aeg. The aeg abstraction is not specific to fence insertion and can also be used for other program analysis tasks.

- A formalisation of the generation of the event structures and candidate executions of a program in the framework of Alglave et al. [2010] (Section 5.5). This has in previous work only been treated informally.

- —An implementation of our approach in the new tool musketeer and an evaluation and comparison of our tool to others (Sections 2 and 7). Our evaluation on both classic examples (such as Dekker's algorithm) and large real-world programs from the Debian GNU/Linux distribution (such as memcached which has about 10,000 LoC) shows that our method achieves good precision and scales well.

- —A study of the performance impact of fences inserted by different fence insertion methods (Sections 2 and 7.3). For this study we implemented several of the competing approaches (such as pensieve).

- —A description of how to insert fences into a C program using inline assembly and taking into account data, address, and control dependencies (Section 7.1).

Outline. We discuss the performance impact of fences in Section 2, and survey related work in Section 3. We give an introduction to axiomatic memory models in Section 4. We detail how we detect critical cycles in Section 5, and how we place fences in Section 6. In Section 7, we report on an experimental comparison between the existing methods and our new tool musketeer. We provide full sources, benchmarks and experimental reports online at http://www.cprover.org/wmm/musketeer.

### 2. MOTIVATION

Before considering elaborate methods for the placement of fences, we investigated whether naive approaches to fence insertion indeed have a negative performance impact.

There is surprisingly little related work; we found [Sura et al. 2005; Marino et al. 2011; Spear et al. 2009; Fang et al. 2003]. Nevertheless, fences are considered to be amongst the most expensive instructions: Herlihy and Shavit [2008] write that "memory barriers are expensive (100s of cycles, maybe more), and should be used only when necessary." Bouajjani et al. [2011] benchmarked x86's mfence (see http://concurrency.informatik.uni-kl.de/trencher.html), and observe that it has a significant cost when used in isolation. Similar observations were made by Alglave and Maranget [2011] (also see http://offence.inria.fr/exp/speed.html).

We measured the overhead of different fencing methods on a stack and a queue from the liblfds lock-free data structure package (http://liblfds.org). For each data structure, we create a harness (consisting of 4 threads) that concurrently invokes its operations.

We built several versions of the above two programs:

- (M) with fences inserted by our tool musketeer;

- (P) with fences following the *delay set analysis* of the pensieve compiler [Sura et al. 2005], i.e., a static over-approximation of Shasha and Snir's eponymous (dynamic) analysis [Shasha and Snir 1988];

- (V) with fences following the *Visual Studio* policy, i.e., guaranteeing acquire/release semantics (in the C11 sense [C11 2011]) for reads and writes of volatile variables (see http://msdn.microsoft.com/en-us/library/vstudio/jj635841.aspx, accessed 04-11-2013). We emphasise that this method does not guarantee SC, and we include it only as a comparison point here. On x86, no fences are necessary to enforce acquire/release semantics, as the model is sufficiently strong already. Hence, we only provide data for ARM.

- —(E) with fences after each access to a shared variable;

- (H) with an mfence (x86) or a dmb (ARM) after every assembly instruction that writes (x86) or reads or writes (ARM) any global or heap-allocated data.

These experiments required us to implement (P), (E), and (V) ourselves, so that they would handle the architectures that we considered. This means in particular that our tool provides the pensieve policy (P) for TSO, Power, and ARM, whereas the original pensieve targeted Java only.

We compiled all the program versions, i.e., both the original program and the program with fences inserted according to the different fencing strategies, with gcc -00. We ran all versions 100 times on an x86-64 Intel Core i5-3570 with 4 cores at 3.40 GHz and

A:4 J. Alglave et al.

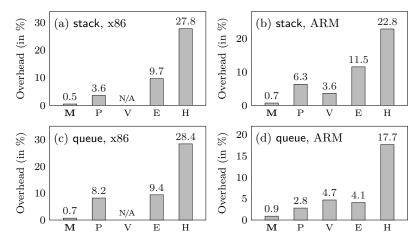

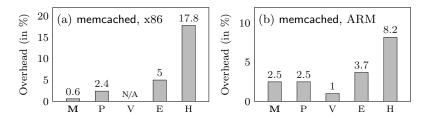

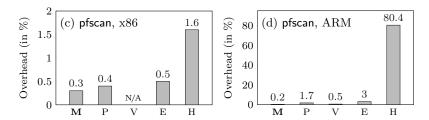

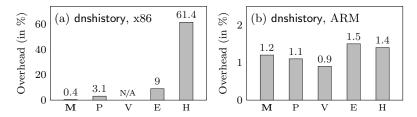

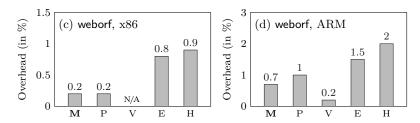

Fig. 1. Overheads for the different fencing strategies.

|     | stack on x86     | stack on ARM     | queue on x86     | queue on ARM     |

|-----|------------------|------------------|------------------|------------------|

| (M) | [10.059; 10.089] | [11.950; 11.973] | [12.296; 12.328] | [21.419; 21.452] |

| (P) | [10.371; 10.400] | [12.608; 12.638] | [13.206; 13.241] | [21.818; 21.850] |

| (V) | N/A              | [12.294; 12.318] | N/A              | [22.219; 22.255] |

| (E) | [10.989; 11.010] | [13.214; 13.259] | [13.357; 13.390] | [22.099; 22.128] |

| (H) | [12.788; 12.838] | [14.574; 14.587] | [15.686; 15.723] | [24.983; 25.013] |

Fig. 2. Confidence intervals for the mean execution times (in sec) for the data structure experiments.

4 GB of RAM, and on an ARMv7 (32-bit) Samsung Exynos 4412 with 4 cores at 1.6 GHz and 2 GB of RAM.

For each program version, Figure 1 gives the mean overhead w.r.t. the unfenced program. We give the overhead (in %) in *user time* (as given by Linux time), i.e., the time spent by the program in user mode on the CPU. Amongst the approaches that guarantee SC (i.e., all but V), the best results were achieved with our tool musketeer.

We checked the statistical significance of the execution time improvement of our method over the existing methods by computing and comparing the confidence intervals for the mean execution times. The sample size is N=100 and the confidence level is  $1-\alpha=95\%$ . The confidence intervals are given in Figure 2. If the confidence intervals for two methods are non-overlapping, we can conclude that the difference between the means is statistically significant.

As discussed later in Section 5.1, the fence insertion approaches compared in this section analyse C programs while assuming a straightforward compilation scheme to assembly in which accesses are not reordered or otherwise optimised by the compiler. Thus, sound results are only achieved when using compilation settings that guarantee these properties (e.g., gcc -00).

Nevertheless, we also compared the approaches when compiling with -01 to get an estimate about how the different approaches would fare when allowing more compiler optimisations. We observed that on x86 the runtime decreased between 1% and 9%. On ARM the runtime decreased between 3% and 31%. The relative performance of the different approaches remained the same as with -00, i.e., the best runtime was achieved with musketeer (M) while the approach H (fence after every access to static or heap memory) was slowest. We give the corresponding data online at http://www.cprover.org/wmm/musketeer.

| authors                  | tool     | model style | objective                 |

|--------------------------|----------|-------------|---------------------------|

| Abdulla et al. [2013]    | memorax  | operational | reachability              |

| Alglave et al. [2010]    | offence  | axiomatic   | SC                        |

| Bouajjani et al. [2013]  | trencher | operational | SC                        |

| Fang et al. [2003]       | pensieve | axiomatic   | SC                        |

| Kuperstein et al. [2010] | fender   | operational | reachability              |

| Kuperstein et al. [2011] | blender  | operational | reachability              |

| Linden and Wolper [2013] | remmex   | operational | reachability              |

| Liu et al. [2012]        | dfence   | operational | specification             |

| Sura et al. [2005]       | pensieve | axiomatic   | $\widetilde{\mathrm{SC}}$ |

| Abdulla et al. [2015]    | persist  | operational | persistence               |

Fig. 3. Overview of existing fence synthesis tools.

### 3. RELATED WORK

The work of Shasha and Snir [1988] is a foundation for much of the field of fence synthesis. Most of the work cited below inherits their notions of *delay* and *critical cycle*. A delay is a pair of instructions in a thread that can be reordered by the underlying architecture. A critical cycle essentially represents a minimal violation of sequential consistency.

Figure 3 classifies the methods that we compare to w.r.t. their style of model (operational or axiomatic). The table further indicates the objective of the fence insertion procedure: enforcing SC, preventing reachability of error states (i.e., ensuring safety properties), or other specifications (such as enforcing given orderings of memory accesses).

We report on our experimental comparison to these tools in Section 7. We now summarise the fence synthesis methods per style. We write TSO for Total Store Order, implemented in Sparc TSO [SPARC 1994] and Intel x86 [Owens et al. 2009]. We write PSO for Partial Store Order and RMO for Relaxed Memory Order, two other Sparc architectures. We write Power for IBM Power [Power 2009].

### 3.1. Operational models

Linden and Wolper [2013] explore all executions (using what they call *automata acceleration*) to simulate the reorderings occurring under TSO and PSO. Abdulla et al. [2013] couple predicate abstraction for TSO with a counterexample-guided strategy. They check if an error state is reachable; if so, they calculate what they call the *maximal permissive* sets of fences that forbid this error state. Their method guarantees that the fences they find are *necessary*, i.e., removing a fence from the set would make the error state reachable again. A precise method for PSO is presented by Abdulla et al. [2015].

Kuperstein et al. [2010] explore all executions for TSO, PSO and a subset of RMO, and along the way build constraints encoding reorderings leading to error states. The fences can be derived from the set of constraints at the error states. The same authors [Kuperstein et al. 2011] improve this exploration under TSO and PSO using an abstract interpretation they call partial coherence abstraction, relaxing the order in the write buffers after a certain bound, thus reducing the state space to explore. Meshman et al. [2014] synthesise fences for infinite-state algorithms to satisfy safety specifications under TSO and PSO. The approach works by refinement propagation: They successively refine the set of inferred fences by combining abstraction refinements of the analysed program. Liu et al. [2012] offer a dynamic synthesis approach for TSO and PSO, enumerating the possible sets of fences to prevent an execution picked dynamically from reaching an error state.

A:6 J. Alglave et al.

Bouajjani et al. [2013] build on an operational model of TSO. They look for *minimum violations* (viz. critical cycles) by enumerating *attackers* (viz. delays). Like us, they use integer linear programming (ILP). However, they first enumerate all the solutions, then encode them as an ILP, and finally ask the solver to pick the least expensive one. Our method directly encodes the whole decision problem as an ILP. The solver thus both constructs the solution (avoiding the exponential-size ILP problem) and ensures its optimality.

Abdulla et al. [2015] investigate a new property called *persistence* as a comprise between optimality and efficiency. A TSO program is persistent if, for any trace t, there exists an SC trace t' in which the program order and store order between events are identical to those in t. If a program is not persistent, the tool persist uses patterns to find *fragility* – the cause of non-persistence – and infers a set of fences.

All the approaches above focus on TSO and its siblings PSO and RMO, whereas we also handle the significantly weaker Power model, including subtle barriers (e.g., lwsync), compared to the simpler meence of x86.

### 3.2. Axiomatic models

Krishnamurthy and Yelick [1996] apply Shasha and Snir's method to *single program multiple data* systems. Their abstraction is similar to ours, except that they do not handle pointers. Moreover, since their programs are symmetrical, their abstraction can be much smaller than in the general case.

Lee and Padua [2001] propose an algorithm based on Shasha and Snir's work. They use dominators in graphs to determine which fences are redundant. This approach was later implemented by Fang et al. [2003] in pensieve, a compiler for Java. Sura et al. later implemented a more precise approach in pensieve [Sura et al. 2005] (see (P) in Section 2). They pair the cycle detection with an analysis to detect synchronisation that could prevent cycles.

Alglave et al. [2010] revisit Shasha and Snir for contemporary memory models and insert fences following a refinement of [Lee and Padua 2001]. Their offence tool handles snippets of assembly code only, where the memory locations need to be explicitly given.

### 3.3. Others

The work of Vafeiadis and Zappa Nardelli [2011] presents an optimisation of the certified CompCert-TSO compiler to remove redundant fences on TSO.

Marino et al. [2011] experiment with an SC-preserving compiler, showing overheads of no more than 34 %. Nevertheless, they state that "the overheads, however small, might be unacceptable for certain applications".

Bender et al. [2015] provide a fence insertion approach to enforce a set of declared orderings between memory accesses. They model the fence synthesis problem as a minimum multi-cut problem on the control flow graph, and determine the set of fences necessary to additionally enforce the orders that are not already enforced by the architecture (in the absence of fences).

Joshi and Kroening [2015] provide a fence synthesis approach based on bounded model checking that aims at deducing a set of fences sufficient to guarantee the assertions in the program. They iteratively consider counterexamples of increasing length, and reduce the problem of finding a set of fences to computing the minimum hitting set over a set of reorderings.

Lustig et al. [2015] describe a dynamic fence insertion approach. Based on a description of the memory model of the source and target architecture, they generate a finite state machine that dynamically translates code compiled for the source memory model to correctly execute on hardware implementing the target memory model.

### 4. AXIOMATIC MEMORY MODELS

Weak memory effects can occur as follows: a thread sends a write to a store buffer, then to a cache, and finally to memory. While the write transits through buffers and caches, reads can occur before the written value is available in memory to all threads.

To describe such situations, we use the framework of Alglave et al. [2010], embracing in particular SC, Sun TSO (i.e., the x86 model [Owens et al. 2009]), Power, and ARM. In this framework, a memory model is specified as a predicate on *candidate executions*. The predicate indicates whether a candidate execution is allowed (i.e., may occur) or disallowed (i.e., cannot occur) on the respective architecture. A candidate execution is represented as a directed graph. The nodes are memory events (reads or writes), and the edges indicate certain relations between the events. For example, a read-from (rf) edge from a write to a read indicates that the read takes its value from that write.

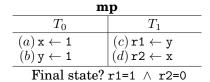

We illustrate this framework in the next section using a *litmus test* (Figure 4). A litmus test is a short concurrent program together with a condition on its final state. The given litmus test consists of two threads, which access shared variables x and y. The shared variables are assumed to be initialized to zero at the beginning. The given condition holds for an execution in which load (c) reads value 1 from y, and load (d) reads value 0 from x. Whether the given litmus test has an execution that can end up in this final state depends on the memory model. For example, the given outcome can occur on Power but not on TSO. Thus, for a given architecture, a set of litmus tests together with the information of whether the given outcome can occur on any execution characterises the architecture.

### 4.1. Basics

We next describe how the set of candidate executions of a program is defined. A candidate execution is obtained by first generating an *event structure*. An event structure  $E \triangleq (\mathbb{E}, po)$  is a set of memory events  $\mathbb{E}$  together with the program order relation po. An *event* is a read from memory or a write to memory, consisting of an identifier, a direction (R for read or W for write), a memory address (represented by a variable name) and a value. The program order po is a per-thread total order over  $\mathbb{E}$ . An event structure represents an execution of the program, assuming the shared reads can return *arbitrary* values.

For example, Figure 5a gives an event structure associated with the litmus test in Figure 4. A store instruction (e.g.,  $x \leftarrow 1$  on  $T_0$ ) gives rise to a write event (e.g., (a)Wx1), and a load instruction (e.g.,  $r1 \leftarrow y$  on  $T_1$ ) gives rise to a read event (e.g., (c)Ry1). In this particular event structure, we have assumed that the load (c) on  $T_1$  read value 1, and the load (d) on  $T_1$  read value 0, but any value for the loads (c) and (d) would give rise to a valid event structure.

An event structure can be completed to a candidate execution by adding an execution witness  $X \triangleq (\mathsf{co},\mathsf{rf},\mathsf{fr})$ . An execution witness represents the communication between the threads and consists of the three relations  $\mathsf{co},\mathsf{rf}$ , and  $\mathsf{fr}$ . The coherence relation  $\mathsf{co}$  is a peraddress total order on write events, and models the memory coherence widely assumed by modern architectures. It links a write w to any write w' to the same address that hits the memory after w. The read-from relation  $\mathsf{rf}$  links a write w to a read r such that r reads the value written by w. The fr relation is defined in terms of  $\mathsf{rf}$  and  $\mathsf{co}$  (hence we say it is a derived relation). A read r is in  $\mathsf{fr}$  with a write w if the write w' from which r reads hits the memory before w. Formally, we have:  $(r,w) \in \mathsf{fr} \triangleq \exists w'.(w',r) \in \mathsf{rf} \land (w',w) \in \mathsf{co}$ .

<sup>&</sup>lt;sup>1</sup>Our notion of event structures differs from the one previously introduced by Winskel [1986]. Winskel's event structures also contain a conflict relation in addition to a set of events and a partial order over them.

A:8 J. Alglave et al.

Fig. 4. Message Passing (mp).

Fig. 5. Event structure and candidate execution

Figure 5b shows the event structure of Figure 5a completed to a candidate execution. A candidate execution is uniquely identified by the event structure E and execution witness X. Inserting fences into a program does not change the set of its candidate executions. For example, if we would place a fence between the two stores of  $T_0$  in Figure 4, the litmus test would still have the same set of candidate executions. However, the fences do affect which of those candidate executions are possible on a given architecture.

Not all event structures can be completed to a candidate execution. For example, had we assumed that the first read in Figure 4 reads value 2, then there would be no execution witness such that the read can be matched up via rf with a corresponding write writing the same value (as there is no instruction writing value 2).

As we have mentioned earlier, a memory model is specified as a predicate on candidate executions. Such a predicate is typically formulated as an acyclicity condition on candidate executions. For example, a candidate execution (E,X) is allowed (i.e., possible) on SC if and only if  $\operatorname{acyclic}(\operatorname{po} \cup \operatorname{co} \cup \operatorname{rf} \cup \operatorname{fr})$ . This means that a candidate execution is not possible on SC if it contains at least one cycle formed of edges from po, co, rf, and fr. Consider for example the candidate execution in Figure 5b. This execution is not possible on SC as it has a cycle.

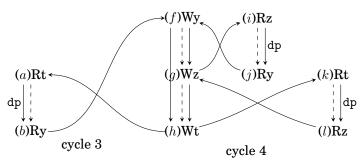

# 4.2. Minimal cycles

Any execution that has a cycle (i.e., a cycle formed of edges in  $po \cup rf \cup co \cup fr$ ) also has a *minimal cycle*. Given a candidate execution (E, X), a minimal cycle is a cycle such that

(MC1) per thread, there are at most two accesses, and the accesses are adjacent in the cycle; and

(MC2) for a memory location  $\ell$ , there are at most three accesses to  $\ell$  along the cycle, and the accesses are adjacent in the cycle.

The reason for (MC1) is that the po relation is transitive. That is, given a cycle with more than two accesses for a thread, the po edge from the first to the last access (according to po) forms a chord in the cycle. This chord can be used to bypass the other accesses from the thread and thus form a smaller cycle containing only two accesses of the thread.

Fig. 6. A cycle in a candidate execution, and two possible shortcuts one can take to form a smaller cycle

The property (MC2) can be seen by careful inspection of the different shapes candidate executions can have, and the shortcuts one can consequently take in cycles. Consider for example Figure 6. Figure 6a shows a cycle involving four accesses to variable x. We know that any two writes to a given variable are connected by a co edge (by the definition of co). Therefore, there either is a co edge from event (a) to event (c) (Figure 6b) or there is a co edge from event (c) to event (a) (Figure 6c). In both cases, we obtain a smaller cycle bypassing one of the accesses to variable x.

We will later extend the notion of minimal cycles to critical cycles, which embody minimal violations of SC (while not violating memory coherence).

### 4.3. Models weaker than SC

In the axiomatic framework of Alglave et al. [2010], a memory model is specified as a predicate on candidate executions. The predicate is phrased as an acyclicity check on a subrelation of po  $\cup$  co  $\cup$  rf  $\cup$  fr. This means that only those executions for which this acyclicity predicate holds are possible on the respective memory model.

The SC model is defined by requiring all relations to be acyclic, i.e.,  $acyclic(po \cup co \cup rf \cup fr)$ . In models weaker than SC, only a proper subrelation of  $po \cup co \cup rf \cup fr$  is required to be acyclic. For a given candidate execution and memory model, we say that those edges which are in  $po \cup co \cup rf \cup fr$  but not in the subrelation are *relaxed*. In the Power model, for example, the program order edges po between events not separated by a fence are not part of the subrelation of  $po \cup co \cup rf \cup fr$  required to be acyclic. Hence, the candidate execution depicted in Figure 5b is possible on Power. We thus say that on Power the program order edges are relaxed.

We define in the following a few further relations over memory events that allow us to specify the edges that are relaxed in a model. All these relations are subrelations of the relations already defined. We write dp (with dp  $\subseteq$  po) for the relation that models dependencies between instructions. For instance, there is a data dependency between a load and a store in an execution when the value written by the store was computed from the value obtained by the load. We further write rfe (resp. coe, fre) for the external read-from (resp. external coherence, external from-read), i.e., when the source and target belong to different threads. We write rfi for the internal read-from, i.e., when the source and target belong to the same thread. The fence relations (such as mfence  $\subseteq$  po) model architecture-specific fences. They connect all events that occur before the fence to all events that occur after the fence.

Relaxed or safe. When a thread can read from its own store buffer [Adve and Gharachorloo 1995] (the typical TSO/x86 scenario), we relax the internal read-from rfi, that is, rf where source and target belong to the same thread. When two threads  $T_0$  and  $T_1$  can communicate privately via a cache (a case of write atomicity relaxation [Adve and Gharachorloo 1995]), we relax the external read-from rfe, and call the corresponding write non-atomic. This is the main particularity of Power and ARM, and cannot happen

A:10 J. Alglave et al.

|      | SC     | x86    | Power                                 |

|------|--------|--------|---------------------------------------|

| poWR | always | mfence | sync                                  |

| poWW | always |        | sync or lwsync                        |

| poRW | always | always | sync or lwsync or dp                  |

| poRR | always | always | sync or lwsync or dp or branch; isync |

Fig. 7. ppo and fences per architecture.

on TSO/x86. Some program order pairs may be relaxed as well (e.g., write-read pairs on x86), i.e., only a subset of po is guaranteed to occur in order. We call this subset the *preserved program order*, ppo. When a relation is not relaxed on a given architecture, we call it *safe*.

Figure 7 summarises ppo per architecture. The columns are architectures, e.g., x86, and the lines are relations, e.g., poWR. We write, e.g., poWR for the program order between a write and a read. We write "always" when the relation is in the ppo of the architecture: e.g., poWR is in the ppo of SC. When we write something else, typically the name of a fence, e.g., mfence, the relation is not in the ppo of the architecture (e.g., poWR is not in the ppo of x86), and the fence can restore the ordering: e.g., mfence maintains write-read pairs in program order.

Following Alglave et al. [2010], the relation fence (with fence  $\subseteq$  po; for some concrete architecture-specific fence) induced by a fence is *non-cumulative* when it only orders certain pairs of events surrounding the fence. The relation fence is *cumulative* when it additionally makes writes atomic, e.g., by flushing caches. In our model, this amounts to making sequences of external read-from and fences (rfe; fence or fence; rfe) safe, but rfe alone would not be safe. In Figure 4, placing a cumulative fence between the two writes on  $T_0$  will not only prevent their reordering, but also enforce an ordering between the write (a) on  $T_0$  and the read (c) on  $T_1$ , which reads from  $T_0$  (in Figure 5b).

Architectures. An architecture A determines the relations safe (i.e., not relaxed) on A. We always consider the coherence co, the from-read relation fr and the fence relations to be safe. SC relaxes nothing, i.e., also rf and po are safe. For example, TSO authorises the reordering of write-read pairs (relaxing po edges from a write event to a read event, i.e., poWR) and store buffering (relaxing rfi edges). Thus, the TSO memory model can be phrased as  $\operatorname{acyclic}((po \setminus poWR) \cup mfence \cup co \cup rfe \cup fr)$ . We refer to Alglave et al. [2014] for a description of the Power memory model.

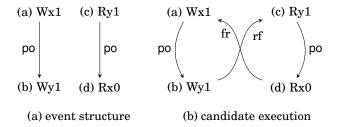

All models we handle satisfy the SC per location property. That is, the edges that are part of cycles that consist of events that access only a single memory location are never relaxed. Formally, we have  $\operatorname{acyclic}(\operatorname{po-loc} \cup \operatorname{co} \cup \operatorname{rf} \cup \operatorname{fr})$ , with po-loc restricted to the po edges between events that access the same memory location. This property models the memory coherence provided by modern architectures. We illustrate it with a litmus test in Figure 8. The two threads access the memory location x, which is assumed to be 0 at the beginning. The condition models whether it is possible for  $T_0$  to first read the new value 1, and then read the old value 0. The corresponding candidate execution is depicted on the right. The execution has a cycle that consists of only one memory location. Therefore, this execution is not possible as the edges in such cycles are never relaxed.

### 4.4. Critical cycles

Following [Shasha and Snir 1988; Alglave and Maranget 2011], for an architecture A, a *delay* is a po or rf edge that is not safe (i.e., is relaxed) on A. A candidate execution (E,X) is valid on A yet not on SC iff

(DC1) it contains at least one cycle that contains a delay, and

Fig. 8. Read-read coherence.

(DC2) all cycles in it contain a delay.

If there would be a cycle that does not contain a delay, then the execution would be invalid both on SC and A. If there would be no cycles at all in the execution, then the execution would be valid on both SC and A.

To enforce SC on a weaker architecture A, we need to insert memory fences into the program such as to disallow the candidate executions that satisfy properties DC1 and DC2. That is, we need to insert fences such that for each such candidate execution at least one cycle is not relaxed. It is not necessary to disallow all cycles in a candidate execution, as ensuring that one cycle is not relaxed is sufficient to disallow an execution.

*Critical cycles*. Any candidate execution that satisfies properties DC1 and DC2 has a cycle, and thus also has a minimal cycle (see Section 4.2). By DC2, the minimal cycle also contains a delay. We refer to such cycles as *critical cycles*. Formally, a critical cycle for architecture *A* is a cycle which has the following characteristics:

(CS1) the cycle contains at least one delay for *A*;

(CS2) per thread, there are at most two accesses, the accesses are adjacent in the cycle, and the accesses are to different memory locations; and

(CS3) for a memory location  $\ell$ , there are at most three accesses to  $\ell$  along the cycle, the accesses are adjacent in the cycle, and the accesses are from different threads.

Thus, a critical cycle is a minimal cycle for which it *additionally* holds that (a) it has at least one delay, (b) the accesses of a single thread are to different memory locations, and (c) the accesses to a given location  $\ell$  are from different threads. In fact, together with the properties MC1 and MC2 of minimal cycles, property (a) implies properties (b) and (c), as we show in the next two paragraphs.

To see that (b) holds, assume we have a minimal cycle for which (a) holds but not (b). Thus, there is a thread in the cycle for which its two accesses are to the same location. Then either (i) there is no additional access in the cycle, or (ii) there is an additional access in the cycle. (i) We have a cycle of length 2. This cycle must involve the two accesses (which are to the same memory location). Such cycles are never relaxed due to memory coherence. The cycle thus does not contain a delay. But this contradicts the initial assumption that the cycle has a delay. Therefore, (b) must hold. (ii) By MC2, this location can occur at most three times in the cycle. The third access must be by a different thread. Since communication edges are always between events operating on the same memory location, it follows that we have a cycle of length 3 that mentions only one memory location (cf. Figure 8). Since these cycles are never relaxed, it follows that the cycle does not have a delay. But this contradicts the initial assumption that the cycle has a delay. Therefore, (b) must hold.

We see that property (c) holds since (b) states that a thread accesses different memory locations. Hence, all accesses to a given location must come from different threads.

A:12 J. Alglave et al.

```

thread_1

thread_2

void thread_1(int input) void thread_2()

int r1;

int r2, r3, r4;

x = input;

r2 = y;

int r1:

int r2, r3, r4;

_Bool tmp;

r3 = z;

r2 = y;

x = input:

tmp = rand():

r4 = x;

if (rand()%2)

r3 = z;

[!tmp%2] goto 1;

end_function

y = 1;

r4 = x;

y = 1;

else

goto 2;

r1 = z:

1: r1 = z;

x = 1;

2: x = 1;

end_function

```

Fig. 9. A C program (left) and its goto-program (right).

As an example, the execution in Figure 5b contains a critical cycle w.r.t. Power, formed by the sequence of edges po, rf, po, fr. The po edge on  $T_0$ , the po edge on  $T_1$ , and the rf edge between  $T_0$  and  $T_1$  are all relaxed on Power. On the other hand, the cycle does not contain an edge that is relaxed on TSO, and it is thus not a critical cycle on TSO.

To forbid executions containing critical cycles, and consequently to enforce SC, one can insert fences into the program to prevent the delays that are part of the cycles. To prevent a po delay, a fence can be inserted between the two accesses forming the delay, following Figure 7. To prevent an rf delay, a cumulative fence must be used (see Section 6 for details). For the example in Figure 4, for Power, we need to place a cumulative fence between the two writes on  $T_0$ , preventing both the po and the adjacent rf edge from being relaxed, and use a dependency or fence to prevent the po edge on  $T_1$  from being relaxed.

### 5. STATIC DETECTION OF CRITICAL CYCLES

We want to synthesise fences to prevent weak behaviours and thus restore SC. As we explained in Section 4, this can be achieved by placing fences such as to prevent the delays along critical cycles of the candidate executions. However, enumerating all candidate executions and looking for critical cycles in each of them separately would not scale beyond small, simple programs.

Therefore, we look for cycles in an over-approximation of all the candidate executions of the program. We hence avoid enumeration of all candidate executions, which would hinder scalability, and get all the critical cycles of all program executions at once. Thus, for example, we can find all fences preventing the critical cycles occurring in two different executions in one step, instead of having to examine the two executions separately.

# 5.1. Abstract event graphs

We analyse concurrent C programs and assign to them the semantics of the underlying hardware memory model. We thus assume a compilation scheme to assembly in which memory accesses are not reordered, introduced, or removed. Our approach is sound when using compilation settings that guarantee these properties, such as -00 with gcc. To analyse a C program, e.g., as given on the left-hand side of Figure 9, we convert it to a *goto-program* (right-hand side of Figure 9), the internal representation of the CProver framework. A goto-program is a sequence of *goto-instructions*, and closely mirrors the C program from which it was generated. We refer to http://www.cprover.org/goto-cc for further details.

The C program in Figure 9 features two threads which can interfere. The first thread writes the argument "input" to x, then randomly writes 1 to y or reads z, and then writes 1 to x. The second thread successively reads y, z and x. In the corresponding gotoprogram, the **if-else** structure has been transformed into a guard with the condition

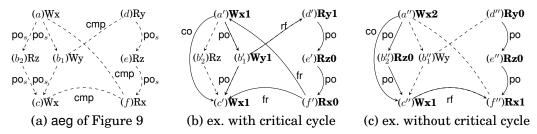

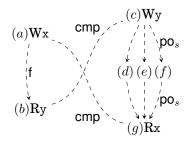

of the **if** followed by a goto construct. From the goto-program, we then compute an abstract event graph (aeg), given in Figure 10(a). The events  $a, b_1, b_2$  and c (resp. d, e and f) correspond to thread<sub>1</sub> (resp. thread<sub>2</sub>) in Figure 9. We only consider accesses to shared variables, and ignore the local variables. We finally explore the aeg to find the potential critical cycles.

An aeg represents all the candidate executions of a program (in the sense of Section 4). Figure 10(b) and (c) give two executions associated with the aeg given in Figure 10(a). For readability, the transitive po edges have been omitted (e.g., between the two events d' and f'). The concrete events that occur in an execution are shown in bold. In an aeg, the events do not have concrete values, whereas in an execution they do. Also, an aeg merely indicates that two accesses to the same variable could form a data race (see the competing pairs (cmp) relation in Figure 10(a), which is a symmetric relation), whereas an execution has oriented relations (e.g., indicating the write that a read takes its value from, see e.g., the rf arrow in Figure 10(b) and (c)). The execution in Figure 10(b) has a critical cycle (with respect to, e.g., Power) between the events a',  $b'_2$ , d', and f'. The execution in Figure 10(c) does not have a critical cycle.

We build an aeg essentially as in [Alglave et al. 2013]. However, our goal and theirs differ: they instrument an input program to reuse SC verification tools to perform weak memory verification, whereas we are interested in automatic fence placement. Moreover, the work of [Alglave et al. 2013] did not present a semantics of goto-programs in terms of aegs, or a proof that the aeg does encompass all potential executions of the program, both of which we do in this section.

### 5.2. Points-to information

In the previous section, we have denoted abstract events as, e.g., (a)Wx, with x being an address specifier denoting a shared variable in the program. However, shared memory accesses are often performed via pointer expressions. We thus use a pointer analysis to compute which memory locations an expression in the program (such as a [i+1] or \*p) might access. The pointer analysis we use is a standard concurrent points-to analysis that we have shown to be sound for our weak memory models in earlier work [Alglave et al. 2011]. The analysis computes for each memory access expression in the goto-program an abstraction of the set of memory locations potentially accessed.

The result of the pointer analysis is for each memory access expression either a set of address specifiers  $\{s_1,\ldots,s_n\}$  (denoting that the expression might access any of the memory locations associated with the specifiers, with  $s_i\neq *$ ), or the singleton set  $\{*\}$  containing the special address specifier \* (denoting that the expression might access any memory location). An address specifier  $s_i\neq *$  might refer to a single memory location or a region of memory locations. A specifier that refers to a region of memory is for example returned for accesses to arrays. That is, expressions a[i] and a[j] accessing a global array a, with  $i\neq j$ , would both be mapped to the same specifier a, denoting the region of memory associated with the array a.

We say that a concrete memory location m and an address specifier s are compatible, written comp(m,s), if m is in the set of memory locations abstracted over by s. For example, comp(m,\*) holds for any memory location m. As another example, if m refers to a location in array a, and specifier s represents that array, then comp(m,s).

Given two address specifiers  $s_1, s_2$ , we similarly write  $comp(s_1, s_2)$  when the intersection between the set of memory locations abstracted by  $s_1$  and the set of memory

<sup>&</sup>lt;sup>2</sup>As pointed out by a reviewer, for our fence insertion approach it may be sufficient to use a pointer analysis that is sound for SC but not for weaker models. While this is not the case for all memory models that could be expressed in the framework of Alglave et al. [2010], it may hold for the models we consider in this paper. A proof of this conjecture remains as future work.

A:14 J. Alglave et al.

Fig. 10. The aeg corresponding to the program in Figure 9 and two executions corresponding to it.

locations abstracted by  $s_2$  is non-empty. For example,  $comp(s_1, *)$  holds for any address specifier  $s_1$ .

Consequently, instead of being associated with a concrete memory location, abstract events have a single address specifier  $s_i$  (which can also be \*). Thus, if the pointer analysis yields a set of address specifiers  $\{s_1, \ldots, s_n\}$  for an expression, the aeg will contain a static event for each. We provide more details in the following sections.

# 5.3. Formal Definition of Abstract Event Graphs

Given a goto-program (such as the one on the right of Figure 9), we build an aeg  $\triangleq (\mathbb{E}_s, \mathsf{po}_s, \mathsf{cmp})$ , where  $\mathbb{E}_s$  is the set of abstract events,  $\mathsf{po}_s$  is the static program order, and cmp are the competing pairs. Given an aeg G, we write respectively  $G.\mathbb{E}_s$ ,  $G.\mathsf{po}_s$  and  $G.\mathsf{cmp}$  for the abstract events, the static program order and the competing pairs of G. The aeg for the program on the right of Figure 9 is given in Figure 10(a).

Abstract events. An abstract event represents all events with same program point, direction (write or read), and compatible memory location. An abstract event consists of first a unique identifier, then the direction specifier (W or R), and then the address specifier. In Figure 10(a), (a)Wx abstracts the events (a')Wx1 and (a'')Wx2 in the executions of Figure 10(b) and (c). Moreover, for example, a static event (a)W\* would also abstract the two events, as \* is compatible with any memory location. We write addr(e) for the address specifier of an abstract event e.

Static program order. The static program order relation  $po_s$  abstracts all the (dynamic) po edges that connect two events in program order and that cannot be decomposed as a succession of po edges in this execution. We write  $po_s^+$  (resp.  $po_s^*$ ) for the transitive (resp. reflexive-transitive) closure of this relation.

We also write  $begin(po_s)$  and  $end(po_s)$  to denote respectively the sets of the first and last abstract events of  $po_s$ . That is, if we imagine the  $po_s$  relation as a directed graph, then  $begin(po_s)$  contains the abstract events in  $po_s$  that do not have incoming edges, and  $end(po_s)$  contains the abstract events that do not have outgoing edges.

Competing pairs. The external communications  $coe \cup rfe \cup fre$  are over-approximated by the competing pairs relation cmp. In Figure 10(a), the cmp edges (a,f),  $(b_1,d)$ , and (c,f) abstract in particular the fre edges (f',c') and (f',a'), and the rfe edge  $(b'_1,d')$  in Figure 10(b). We do not need to represent internal communications as they are already covered by  $po^+_-$ .

The cmp construction is similar to the first steps of static data race detection (see, e.g., [Kahlon et al. 2009, Sec. 5]), where statements involved in write-read or write-write communications are collected. As further work, we could reduce the set of competing

<sup>&</sup>lt;sup>3</sup>We denote the function composition operator by ∘.

```

(1) assignment: lhs = rhs; i

\tau[lhs = rhs; i](aeg) =

let \mathbb{E}'_s = aeg.\mathbb{E}_s \cup \text{evts}(lhs) \cup \text{evts}(rhs) \cup

trg(lhs) in

let po_s' = aeg.po_s \cup

end(aeg.po_s) \times (evts(rhs) \cup evts(lhs)) \cup

(\operatorname{evts}(rhs) \cup \operatorname{evts}(lhs)) \times \operatorname{trg}(lhs)

in

\tau[i](\mathbb{E}'_s, \mathsf{po}_s', aeg. \mathsf{cmp})

(2) function call<sup>3</sup>: fun(); i

-\operatorname{po}_{s} \to \tau[\operatorname{body}(f)] - \operatorname{po}_{s} \to \tau[i]

\tau[fun(); i] = \tau[i] \circ \tau[body(fun)]

(3) guard: [guard] i_1; i_2

\tau[[guard] i_1; i_2](aeg) =

let guarded = \tau[i_1](aeg) in

let \mathbb{E}'_{s}

= aeg.\mathbb{E}_s \cup \mathbf{guarded}.\mathbb{E}_s in

= aeg.\mathsf{po}_s \cup \mathsf{guarded.po}_s in

let po<sub>s</sub>'

\tau[i_2](\mathbb{E}'_s,\mathsf{po}_s',aeg.\mathsf{cmp})

(4) unconditional forward jump: goto l; i

\tau[goto\ l;i] = \tau[follow(l)]

(5) conditional backward jump: l: i_1; [cond] \text{ goto } l; i_2

\tau[l:i_1;[cond] \text{ goto } l;i_2](aeg) =

let local = \tau[i_1](aeg) in

let \mathbb{E}'_s = aeg.\mathbb{E}_s \cup local.\mathbb{E}_s in

\underset{--}{\operatorname{po}_s} \underset{\boldsymbol{\to} \boldsymbol{\tau}[i_1]}{\operatorname{po}_s} - \underset{--}{\operatorname{po}_s} \underset{\boldsymbol{\to} \boldsymbol{\tau}[i_2]}{\operatorname{res}}

let po_s' = aeg.po_s \cup local.po_s \cup end(local.po_s)

\times begin(local.po_s) in

\tau[i_2](\mathbb{E}'_s,\mathsf{po}_s',aeg.\mathsf{cmp})

```

Fig. 11. Operations to create the aeg of a goto-program.

A:16 J. Alglave et al.

(6) assume / assert / skip: {assume, assert}( $\phi$ ); i / skip; i

```

\begin{aligned} \tau[\, assume(\phi); i] &= \tau[i] \\ \tau[\, assert(\phi); i] &= \tau[i] \end{aligned} \\ \tau[\, skip; i] &= \tau[i] \end{aligned}

```

(7) atomic section: atomic\_begin;  $i_1$ ; atomic\_end;  $i_2$

```

\begin{split} \tau[atomic\_start; i_1; atomic\_end; i_2](aeg) = \\ \textbf{let} \ section = \ \tau[i_1]((aeg.\mathbb{E}_s \cup \{\mathsf{f}\}, \\ & aeg.\mathsf{po}_s \cup \mathsf{end}(aeg.\mathsf{po}_s) \times \{\mathsf{f}\}, \\ & aeg. \, \mathsf{cmp})) \ \textbf{in} \\ & -\overset{\mathsf{po}_s}{-} \xrightarrow{\mathsf{f}} \ -\overset{\mathsf{po}_s}{-} \xrightarrow{\mathsf{f}} \tau[i_1] -\overset{\mathsf{po}_s}{-} \xrightarrow{\mathsf{f}} \tau[i_2]} \\ \textbf{let} \ \mathsf{po}_s' = \ section.\mathsf{po}_s \cup \, \mathsf{end}(\mathsf{section}.\mathsf{po}_s) \times \{\mathsf{f}\} \ \textbf{in} \\ & \tau[i_2]((\mathsf{section}.\mathbb{E}_s, \mathsf{po}_s', \mathsf{section}.\, \mathsf{cmp})) \end{split}

```

(8) new thread: start\_thread *th*; *i*

```

\tau[start\_thread\ th;i](aeg) =

\mathbf{let}\ local\ =\ \tau[\mathsf{body}(th)](\bar{\emptyset})\ \mathbf{in}

\mathbf{let}\ main\ =\ \tau[i](aeg)\ \mathbf{in}

--\overset{\mathsf{po}_s}{--}\to\tau[i]\cdot--\overset{\mathsf{cmp}}{--}\to\tau[\mathsf{body}(f)]

\mathbf{let}\ inter\ =\ \tau[i](\bar{\emptyset})\ \mathbf{in}

(local.\mathbb{E}_s\cup \mathsf{main}.\mathbb{E}_s,\ local.\mathsf{po}_s\cup \mathsf{main}.\mathsf{po}_s,\ local.\mathbb{E}_s\otimes \mathsf{inter}.\mathbb{E}_s)

```

(9) end of thread: end\_thread;

$\tau[end\_thread](aeg) = aeg$   $\emptyset$

Fig. 12. Operations to create the aeg of a goto-program (continued).

pairs using a synchronisation analysis, as in, e.g., [Sura et al. 2005]. If we assume the correctness of locks for example, some threads might never interfere.

*Fences*. In the aeg, we encode memory fences as special abstract events – i.e., as nodes in the graph. We write f for a full fence (e.g., mfence in x86, sync in Power, dmb in ARM), lwf for a lightweight fence (e.g., lwsync in Power), cf for a control fence (e.g., isync in Power, isb in ARM).

In [Alglave et al. 2010], fences are modelled as a relation *fenced* between concrete events. We did not use this approach, since a fence can then correspond to several edges and we would need an additional relation over our abstract event relations to keep

```

int local1=x;

mov r, #x

local1=local1flocal1;

ldr r1,[r, #0]

exors r1, r1, r1

exors r1, r1, r1

int local2=*(&y + local1);

mov r2, #y

mov r3 [r2, r1]

```

Fig. 13. A fragment of C program (left) with two shared variables x and y, and a possible straightforward translation in ARM assembly (right).

track of the placement of fences. The effect of fences is interpreted during the cycle search in the aeg.

Dependencies form a relation between abstract events that is maintained outside of the aeg. They are calculated in musketeer from the input program on the C level. Dependencies relate two accesses to shared memory at the assembly level via registers. As we analyse C programs and we make no assumption regarding the machine or the compiler used, neither the assembly translation nor the use of registers between shared memory accesses is unique or provided to us. For example, there is a dependency between x and y in the program fragment presented in Figure 13 (left), since a straightforward translation to assembly could generate a dependency. For example, in ARM assembly, we can translate this C program to the assembly code in Figure 13 (right), where a dependency by address between x and y was intentionally placed via the register r1. The register r1 always holds 0 after the interpretation of the exclusive disjunction on the value of x, and this 0 is added to the pointer to y before being dereferenced in register r3. Processors ignore that the value is always 0 and enforce a dependency.

Compiler optimisations can, however, remove these dependencies. In the tool musketeer, we provide the option *-no-dependencies* which safely ignores all these calculated dependencies in the aeg. Under this option, dependencies or fences might be spuriously inserted in places where an actual dependency already exists.

The same consideration applies to dependency generation, as we will treat in detail in Subsection 7.1.

# 5.4. Constructing Abstract Event Graphs from C Programs

We define a semantics of goto-programs in terms of abstract events, static program order and competing pairs. We give this semantics below by means of a case split on the type of the goto-instructions. Each of these cases is accompanied in Figures 11 and 12 by a graphical representation summarising the aeg construction on the right-hand side, and a formal definition of the semantics on the left-hand side. We assume that forward jumps are unconditional and that backward jumps are conditional. Conditional forward jumps can be "simulated" by those two instructions.

The construction of the aeg from a goto-program is implemented by means of a case split over the type of goto-instruction. The algorithm is outlined in Figure 15 (left side). We give further details about the algorithmin Section 5.7.

In Figures 11 and 12, we write  $\tau[i]$  and  $\tau[i_1; \ldots; i_n]$  to represent the semantics of a goto-instruction i and a sequence of goto-instructions  $i_1; \ldots; i_n$ , respectively. Other notations, e.g., follow(f) or body(f), are explained below. We do not compute the values of the variables, and thus do not interpret the expressions. In Figure 10(a), (a)Wx represents the assignment "x = input" in thread 1 in Figure 9 (since "input" is a local variable). This abstracts the values that "input" could hold, e.g., 1 (see (a')Wx1 in Figure 10(b))

$<sup>\</sup>overline{^4}$ We keep track of the relations between local and shared variables per thread to calculate a dependency relation.

A:18 J. Alglave et al.

or 2 (see (a'')Wx2 in Figure 10(c)). Prior to building the aeg, we copy expressions of conditions or function arguments into local variables. Thus, communication via shared variables can occur in the assignment case only.

We now present the construction of the aeg starting with the intra-thread instructions (e.g., assignments, function calls), creating static events and  $\mathsf{po}_s$  edges, and then the thread constructor, creating cmp edges. We write  $G = \mathsf{aeg}(P) = \tau[P](\bar{\emptyset})$  for the aeg G corresponding to program P. The program P is a sequence of goto-instructions, and  $\bar{\emptyset}$  denotes the empty aeg.

Assignments lhs=rhs. We decompose this statement into sets of abstract events: the reads from potential shared variables in rhs and lhs, denoted by evts(rhs) and evts(lhs), and the writes to the potential target objects trg(lhs). We do not assume any order in the evaluation of the variables in an expression. Hence, we connect to the incoming po<sub>s</sub> all the reads of rhs and all the reads of lhs except trg(lhs). We then connect each of them to the potential target writes trg(lhs). The functions evts() and trg() return sets of abstract events with address specifiers according to the pointer analysis (cf. Section 5.2).

We also record the data and address dependencies between abstract events. For instance, if we have int r1=x; int r2=r1; \*(&y+r2)=1 we know that the abstract event Rx from the rhs of the first instruction is in dependency with the write to r2 (via the use of r1). Moreover, the Wa issued by the last statement (with the address specifier a corresponding to the expression \*(&y+r2)) depends on r2, and thus there is a dependency between Rx and Wa.

Function calls fun(). We build the  $po_s$  corresponding to the function's body (written body(fun)). We then replace the call to a function fun() by its body. This ensures a better precision, in the sense that a function can be fenced in a given context and unfenced in another. In our tool musketeer, recursive functions must be inlined up to a bound. musketeer issues warnings when encountering recursive functions.

*Guarded statement*. We do not keep track of the values of the variables at each program point. Thus we cannot evaluate the guard of a statement. Hence, we abstract the guard and make this statement non-deterministically reachable, by adding a second  $po_s$  edge, bypassing the statement.

Unconditional forward jump to a label L. We connect the previous abstract events to the next abstract events that we generate from the program point L. In Figure 11, we write follow(L) for the sequence of statements following the label L.

Conditional backward jump. A conditional backward jump is a jump to a label already visited. It arises from loops in the program. We copy and append the  $po_s$  subgraph between the label and the goto twice, and connect the last abstract event of the copy to the first abstract event of the original body with a  $po_s$  edge. In Figure 11, begin(S) and end(S) are respectively the sets of the first and last abstract events of the  $po_s$  sub-graph S. We assume that the statement denoted by  $i_1$  (i.e., the body of the loop) does not contain a jump statement that jumps outside of the body.

Assumption, assertion, skip. Similarly to the guarded statement, as we cannot evaluate the condition, we abstract the assumptions and assertions by bypassing them. They are thus handled the same as the skip statement.

Atomic sections. The atomic sections in a goto-program model idealised atomic sections without having to rely on the correctness of their implementation. In the CProver framework, we use the constructs \_\_CPROVER\_atomic\_begin and \_\_CPROVER\_atomic\_end. Atomic sections are used in many theoretical concurrency and verification works. For example, we use them (see Section 7) for copying data to atomic structures, as in,

Fig. 14. From C programs to aegs and candidate executions

e.g., our implementation of the Chase-Lev queue [Chase and Lev 2005] or for implementing compare-and-swaps, as in, e.g., our implementation of Michael and Scott's queue [Michael and Scott 1996].

In this work we overapproximate atomic sections by only considering the effect on memory ordering of entering and leaving a critical section. We do not model the atomicity aspect of atomic sections. Also handling this aspect could improve performance and precision as less (spurious) interferences have to be considered.

We model atomic sections by placing two full fences, written f in Figure 12, right after the beginning of the section and just before the end of the section.

Construction of cmp. We also compute the competing pairs that abstract external communications between threads. For each abstract event with address specifier s, we augment the cmp relation with pairs made of this abstract event and abstract events from an interfering thread with a compatible address specifier s' (i.e., the sets of memory locations represented by s and s' overlap). One of the two accesses needs to be a write. These cmp edges abstract the relations coe, fre, and rfe.

In Figure 12, we use  $\otimes$  to construct the cmp edges when a new interfering thread is spawned. That is, when the goto-instruction start\_thread is met. We define  $\otimes$  as  $A \otimes B = \{(a,b) \in A \times B \mid \mathsf{comp}(\mathsf{addr}(a), \mathsf{addr}(b)) \land (\mathsf{write}(a) \lor \mathsf{write}(b))\}$ . We write  $\emptyset$  for the triple  $(\emptyset, \emptyset, \emptyset)$  representing the empty aeg.

# 5.5. Correctness of the aeg construction

In this section, we explain why the aeg constructed with the transformers of Figures 11 and 12 captures all the candidate executions of a program. As a consequence, if we search for cycles in the aeg we can find all corresponding cycles that might occur in a concrete execution.

Given a goto-program, we want to show that for any event structure that could be derived from it and for any candidate execution valid for this event structure, the sets

A:20 J. Alglave et al.

of events  $(\mathbb{E})$  and all the relations (po, rf, fr, co) are contained (in a sense defined in the following paragraph) in their static counterparts  $\mathbb{E}_s$ ,  $\mathsf{po}_s^+$ , and  $\mathsf{cmp}$ . We need here the transitive closure of  $\mathsf{po}_s$  as the po relation of a concrete execution is transitive, but the static program order relation  $\mathsf{po}_s$  of an  $\mathsf{aeg}$  is not transitive.

We refer in the following to  $\mathbb{E}_s$  as the set of static events, and to  $\mathbb{E}$  as the set of dynamic events. Similarly, we refer to  $\mathsf{po}_s$  as the static program order, and to  $\mathsf{po}$  as the dynamic program order. The reason why we choose the terms static and dynamic is that  $\mathbb{E}_s$ ,  $\mathsf{po}_s$ , and cmp are computed by our static analysis, whereas  $\mathbb{E}$ ,  $\mathsf{po}$ ,  $\mathsf{rf}$ ,  $\mathsf{fr}$ , and co refer to the events and relations that represent a concrete candidate execution. We further use the symbols se and srel to refer to a set of static events and a static relation, respectively.

To map the static events to dynamic events, and relations over static events to relations over dynamic events, we define  $\gamma: \wp(\mathbb{E}_s \times \mathbb{E}_s) \to \wp(\mathbb{E} \times \mathbb{E})$  which *concretises* a static relation as the union of all the dynamic relations that it could correspond to, and  $\gamma_e: \wp(\mathbb{E}_s) \to \wp(\mathbb{E})$  which concretises a set of static events as the union of all the sets of dynamic events that they could correspond to.<sup>5</sup> These two functions are a formalisation of how we interpret aegs.

More formally, we define  $\gamma_e(se) \triangleq \{e' \mid \exists e \in se \text{ s.t. comp}(\text{addr}(e), \text{addr}(e')) \land \text{dir}(e) = \text{dir}(e') \land \text{origin}(e) = \text{origin}(e')\}$ , where origin(a) returns the syntactical object in the source code from which either a concrete or abstract event was extracted. In this definition e' is a concrete event whereas e is a static event. The function comp(addr(e), addr(e')) indicates whether the memory address accessed by e' and the address specifier of e are compatible (i.e., whether the result addr(e) computed by the pointer analysis includes the memory address addr(e'); see Section 5.2 for details). The function dir() (for direction) indicates whether the static event or event given is a read or write. Thus, dir(e) = dir(e') requires that the static event and the concrete event are either both reads or both writes. We use  $\gamma_e$  to define  $\gamma$ :  $\gamma(srel) \triangleq \{(c_1, c_2) \mid \exists (s_1, s_2) \in srel \text{ s.t. } (c_1, c_2) \in \gamma_e(\{s_1\}) \times \gamma_e(\{s_2\})\}$ . In this definition  $c_1, c_2$  are concrete events and  $s_1, s_2$  are static events. We next show a lemma about  $\gamma_e$  and  $\gamma$  that we will use later on.

LEMMA 5.1. Let

$$\mathbb{E}_1 \subseteq \gamma_e(\mathbb{E}_{s,1})$$

and  $\mathbb{E}_2 \subseteq \gamma_e(\mathbb{E}_{s,2})$ . Then  $\mathbb{E}_1 \times \mathbb{E}_2 \subseteq \gamma(\mathbb{E}_{s,1} \times \mathbb{E}_{s,2})$ .

PROOF. Let  $(c_1,c_2)\in\mathbb{E}_1\times\mathbb{E}_2$ . Then  $c_1\in\gamma_e(\mathbb{E}_{s,1})$  and  $c_2\in\gamma_e(\mathbb{E}_{s,2})$ . Using the definition of  $\gamma_e$ , there are  $s_1,s_2$  such that  $c_1\in\gamma_e(\{s1\})$  and  $c_2\in\gamma_e(\{s_2\})$ . Then, since  $(s_1,s_2)\in\mathbb{E}_{s,1}\times\mathbb{E}_{s,2}$ , it follows by the definition of  $\gamma$  that  $(c_1,c_2)\in\gamma(\mathbb{E}_{s,1}\times\mathbb{E}_{s,2})$ .  $\square$

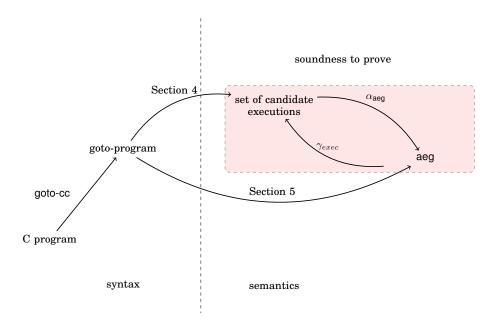

Figure 14 shows the relationship between goto-programs, candidate executions, and aegs. In our proof, we show that for a given program, any execution of that program has its events and relations contained in the  $\gamma_e$ ,  $\gamma$  of the corresponding aeg.

To go from goto-programs to a set of event structures (and then a set of candidate executions), we describe formally how the event structures can be generated. This is a formalisation of the informal description of how event structures are generated from a program as described in Section 4.

For the definition of the assignment case we make use of the function dyn\_evts(1hs = rhs). It takes an assignment statement, and returns all possible events it might correspond to in a concrete execution. For example, for x=\*p+z, we have

$$\mathbf{dyn\_evts}(\mathbf{x=*p+z}) = \bigcup_{i=1,\dots,n} \{(Wxv_1,\{Ry_iv_2,Rzv_3\}) \mid v_1 = v_2 + v_3\}$$

$<sup>^{5}</sup>$ We usually use  $\gamma_e$  with a singleton set (containing one static event) as an argument.

<sup>&</sup>lt;sup>6</sup>The function origin is dual to evts, which returns events given an expression or instruction.

That is, dyn\_evts() yields a set of pairs with the first component being the write event, and the second component being the set of read events. Moreover,  $y_1, \ldots, y_n$  are the concrete memory locations the pointer p might point to according to the pointer analysis. We thus presuppose a correct pointer analysis (cf. Section 5.2).

We next formalise the generation of event structures from a given program P (cf. Section 4) by means of the function  $\sigma$  (which is analogous to  $\tau$  for the aeg construction). We write  $S(P) = \sigma(P)(\emptyset)$  for the set of event structures of a program P, with  $\emptyset$  denoting the empty set of event structures.

Definition 5.2 (event structure semantics S for goto-programs). We write ses for a set of event structures. We define the semantics as follows:

(1) assignment:

```

\begin{split} &\sigma[lhs=rhs;i](\texttt{ses}) = \\ &\textbf{let} \ de = \texttt{dyn\_evts}(lhs=rhs) \ \textbf{in} \\ &\textbf{let} \ \texttt{ses}' = \bigcup_{es \in \texttt{ses}} (\bigcup_{(t,r) \in de} \{(es.\mathbb{E} \cup \{t\} \cup r, es.\texttt{po} \cup \texttt{end}(es.\texttt{po}) \times r \cup r \times \{t\})) \ \textbf{in} \\ &\sigma[i](\texttt{ses}') \end{split}

```

(2) function call:

$$\sigma[fun(); i] = \sigma[i] \circ \sigma[body(fun)]$$

(3) guarded statement:

$$\sigma[[guard]i_1;i_2](ses) =$$

**let**  $ses' = \sigma[i_1](ses) \cup ses$  **in**

$\sigma[i_2](ses')$

(4) unconditional forward jump:

```

\sigma[goto\ l;i] = \sigma[follow(l)]

```

(5) conditional backward jump $^7$ :

```

\begin{split} \sigma[l:i_1;[cond]\mathbf{goto}\ l;i_2](\mathbf{ses}) &= \\ \bigcup_{n\in\mathbb{N}} \sigma[i_2](\sigma[i_1]^n(\mathbf{ses})) \end{split}

```

(6) assume/assert/skip:

```

\sigma[assume(\phi); i] = \sigma[i]

```

(7) atomic section:

```

\begin{split} &\sigma[atomic\_start; i_1; atomic\_end; i_2](\texttt{ses}) = \\ &\textbf{let section} = \sigma[i_1](\bigcup_{es \in \texttt{ses}} \{(es.\mathbb{E} \cup \{\texttt{f}\}, es.\texttt{po} \cup \texttt{end}(es.\texttt{po}) \times \{\texttt{f}\})\}) \textbf{ in} \\ &\sigma[i_2](\bigcup_{es \in \texttt{section}} \{(es.\mathbb{E}, es.\texttt{po} \cup \texttt{end}(es.\texttt{po}) \times \{\texttt{f}\})\}) \end{split}

```

(8) new thread:

```

\begin{split} \sigma[start\_thread\ th; i](\texttt{ses}) &= \\ \textbf{let}\ local &= \sigma[body(th)](\emptyset)\ \textbf{in} \\ \textbf{let}\ main &= \sigma[i](\texttt{ses})\ \textbf{in} \end{split}

```

```

\overline{{}^7\text{We use }f^n(x)} to denote \underbrace{f(\ldots f(x))}_{n \text{ times}}.

```

A:22 J. Alglave et al.

$$\bigcup_{es_1 \in local, es_2 \in main} \{(es_1.\mathbb{E} \cup es_2.\mathbb{E}, es_1.\mathsf{po} \cup es_2.\mathsf{po})\}$$

(9) end of thread:

$$\sigma[end\_thread](ses) = \bigcup_{es \in ses} \{(es.\mathbb{E}, es.po^+)\}$$

Similarly as for aegs, begin(po) and end(po), respectively, denote the sets of events that have no incoming po edges or no outgoing po edges.

The guards are not interpreted by this semantics, meaning that there may be event structures that do not correspond to an actual execution of the program, regardless of the architecture. For example, even if an if-condition could never be satisfied, an event structure passing through the body of this if-statement would be constructed. These kinds of event structures are thus spurious. However, since this is an overapproximation we still arrive at a correct soundness argument if we can show that all those event structures are contained in the aeq.

Using this formalisation, we can establish that, for each event structure of a gotoprogram, we can find po edges and events, abstracted by  $po_s^+$  edges and abstract events in the aeg (Lemma 5.3). This can be proven by structural induction over the event structure transformers of Definition 5.2 and the corresponding aeg transformers of Figures 11 and 12. We then need to show that for each candidate execution that corresponds to an event structure of the goto-program, all the communication relations (rf, co, and fr) are captured by the cmp relation in the aeg (Lemma 5.4). More precisely, we want to establish the three properties below:

PROPERTY 1 (SOUNDNESS). Let P be a program, let  $E \in S(P)$  and let X = (ff, co, fr) be an execution witness. Let further G = aeg(P). Then the  $aeg\ G$  soundly captures (E, X) if the following properties hold:

$$\gamma(G.\mathsf{po}_s^+) \supseteq E.\mathsf{po} \cup X.\mathsf{coi} \cup X.\mathsf{rfi} \cup X.\mathsf{fri},$$

(1)

$$\gamma(G. \mathit{cmp}) \supseteq X.\mathit{coe} \cup X.\mathit{rfe} \cup X.\mathit{fre},$$

(2)

$$\gamma_e(G.\mathbb{E}_s) \supseteq E.\mathbb{E},$$

(3)

The property above corresponds to  $\gamma_{exec}$  from Figure 14. That is,  $\gamma_{exec}$  works by concretising the static relations  $G.\mathsf{po}_s^+$  and  $G.\mathsf{cmp}$  via  $\gamma$ , and the set of static events  $G.\mathbb{E}_s$  via  $\gamma_e$ .

LEMMA 5.3 (EVENTS AND PO). For any event structure  $E \in S(P)$ , and aeg G = aeg(P) we have  $E.\mathbb{E} \subseteq \gamma_e(G.\mathbb{E}_s)$  and  $E.po \subseteq \gamma(G.po_s^+)$ .

PROOF. The proof works by structural induction over the input program P, and thus by considering each event structure transformer in Definition 5.2, and the corresponding aeg transformer in Figures 11 and 12. We use the notation  $\operatorname{ses} \ll G \triangleq \forall E \in \operatorname{ses} : E.\mathbb{E} \subseteq \gamma_e(G.\mathbb{E}_s) \land E.\operatorname{po} \subseteq \gamma(G.\operatorname{po}_s^+)$  in the following. We further define  $\operatorname{Prop}(P) \triangleq \forall \operatorname{ses}, G : \operatorname{ses} \ll G \Rightarrow \sigma[P](\operatorname{ses}) \ll \tau[P](G)$ . We thus prove in the following that for all input programs P the predicate  $\operatorname{Prop}(P)$  holds.

The base case of the induction is the "end of thread" case. Assume ses  $\ll G$ . The only change the concrete transformer for the  $end\_thread$  case makes to ses is making the porelation of the contained event structures transitive. The aeg transformer for  $end\_thread$  does not change the aeg G. Since in the definition of  $\ll$  the transitive closure of the static program order relation of the aeg is taken it follows that  $\sigma[end\_thread](ses) \ll \tau[end\_thread](G)$  holds.

In the induction step for each case, we can assume the predicate Prop for the constituents of the respective code fragment. For example, in the assignment case lhs := rhs; i (cf. Figure 11 and Definition 5.2) we can assume Prop(i).

Exemplary for all the cases, we show below the proof steps for the assignment case and the conditional backward jump case (which is used to implement loops).

Assignment transformer. We show Prop(lhs := rhs; i). Let Prop(i) hold. Let ses be a set of event structures and let G be an aeg such that ses  $\ll G$ . Let  $es \in ses$ , let st = "lhs = rhs", and let  $(t, r) \in dyn\_evts(st)$ .

We first show the set inclusion for the set of events and the set of concretised static events. We use the abbreviation  $\operatorname{evts} = \operatorname{evts}(lhs) \cup \operatorname{evts}(rhs)$  in the following. We have to show that  $es'.\mathbb{E} = es.\mathbb{E} \cup \{t\} \cup r \subseteq \gamma_e(G.\mathbb{E}_s \cup \operatorname{evts} \cup \operatorname{trg}(lhs)) = \gamma_e(G'.\mathbb{E})$ . By the definition of  $\gamma_e$  we get  $\gamma_e(G'.\mathbb{E}) = \gamma_e(G.\mathbb{E}_s) \cup \gamma_e(\operatorname{evts}) \cup \gamma_e(\operatorname{trg}(lhs))$ . By the assumption of  $\operatorname{ses} \ll G$  we have  $es.\mathbb{E} \subseteq \gamma_e(G.\mathbb{E}_s)$ . By the correctness of the pointer analysis, we further have  $r \subseteq \gamma_e(\operatorname{evts})$  and  $\{t\} \subseteq \gamma_e(\operatorname{trg}(lhs))$ . We thus have  $es'.\mathbb{E} \subseteq \gamma_e(G'.\mathbb{E})$ .

further have  $r\subseteq \gamma_e(\operatorname{evts})$  and  $\{t\}\subseteq \gamma_e(\operatorname{trg}(lhs)).$  We thus have  $es'.\mathbb{E}\subseteq \gamma_e(G'.\mathbb{E}).$  We next show the set inclusion for the program order relation and the concretised static program order relation. We have to show that  $es'.\mathsf{po}=es.\mathsf{po}\cup\operatorname{end}(es.\mathsf{po})\times r\cup r\times\{t\}\subseteq \gamma(G.\mathsf{po}_s\cup\operatorname{end}(G.\mathsf{po}_s)\times\operatorname{evts}\cup\operatorname{evts}\times\operatorname{trg}(lhs))=\gamma(G'.\mathsf{po}_s).$  By the definition of  $\gamma$  we have  $\gamma(G'.\mathsf{po}_s)=\gamma(G.\mathsf{po}_s)\cup\gamma(\operatorname{end}(G.\mathsf{po}_s)\times\operatorname{evts})\cup\gamma(\operatorname{evts}\times\operatorname{trg}(lhs)).$  By the assumption of  $ses\ll G$  we have  $es.\mathsf{po}\subseteq\gamma(G.\mathsf{po}_s).$  Thus, we also have  $\operatorname{end}(es.\mathsf{po})\subseteq\gamma(e\operatorname{end}(G.\mathsf{po}_s)).$  By Lemma 5.1 we thus get  $\operatorname{end}(es.\mathsf{po})\times r\subseteq\gamma(\operatorname{end}(G.\mathsf{po}_s)\times\operatorname{evts})$  and  $r\times\{t\}\subseteq\gamma(\operatorname{evts}\times\operatorname{trg}(lhs)).$  We thus have  $es'.\mathsf{po}\subseteq\gamma(G'.\mathsf{po}_s).$

Let ses' denote the set of event structures resulting from applying the assignment transformer to all event structures in ses. Since we have above chosen  $es \in ses$  arbitrarily we have  $ses' \ll G'$ . Then by assumption of Prop(i) we get  $\sigma[i](ses') \ll \tau[i](G')$ .

Conditional backward jump transformer. The concrete transformer for the conditional backward jump case (Definition 5.2) involves an infinite union over the number of times the loop body is executed. We show that for any number of iterations n, the resulting event structures are contained in the concretisation of the corresponding aeg.